Thursday, November 26th 2009

Elpida Ships Samples of x32-bit I/O 2-Gigabit DDR2 SDRAM

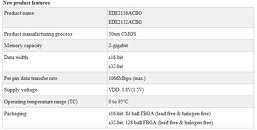

Elpida Memory, Inc., Japan's leading global supplier of Dynamic Random Access Memory (DRAM), today announced that it had begun sample shipments of a 2-gigabit x32-bit I/O DDR2 SDRAM that operates up to a high speed of 1066 Mbps. The new memory device is capable of meeting the need for 1.8V x32-bit and x16-bit I/O as well as low-voltage 1.5V x32-bit and x16-bit I/O.

Rapid advances in the image quality and functionality of digital TV, digital still cameras and other new digital consumer equipment have led to a growing need for memory that can deliver faster speeds, higher densities and wide-bit configurations. Elpida's newly developed 2-gigabit density x32-bit I/O product provides an optimal solution for these needs. Systems with a 32-bit CPU that require 2-gigabit memory density have until now had rely on a conventional 1-gigabit x16-bit I/O two-chip design. Elpida's new 2-gigabit x32-bit I/O product, however, reduces by half the number of mounted memory chips, simplifies high-speed memory bus design, conserves chip mounting space and lowers power consumption.Also, the new DDR2 SDARM is designed to operate at standard 1.8V as well as 1.5V and is well suited to meeting the need for low-power devices for use in mobile devices.

Volume production is scheduled to begin in the second quarter (April-June) of CY 2010.

Rapid advances in the image quality and functionality of digital TV, digital still cameras and other new digital consumer equipment have led to a growing need for memory that can deliver faster speeds, higher densities and wide-bit configurations. Elpida's newly developed 2-gigabit density x32-bit I/O product provides an optimal solution for these needs. Systems with a 32-bit CPU that require 2-gigabit memory density have until now had rely on a conventional 1-gigabit x16-bit I/O two-chip design. Elpida's new 2-gigabit x32-bit I/O product, however, reduces by half the number of mounted memory chips, simplifies high-speed memory bus design, conserves chip mounting space and lowers power consumption.Also, the new DDR2 SDARM is designed to operate at standard 1.8V as well as 1.5V and is well suited to meeting the need for low-power devices for use in mobile devices.

Volume production is scheduled to begin in the second quarter (April-June) of CY 2010.

5 Comments on Elpida Ships Samples of x32-bit I/O 2-Gigabit DDR2 SDRAM

2./ Few memory chips needed... saves cost on manufacturing the chip... and saves cost on installing (soldering) the chip onto OEM PCBs

3./ Smaller PCB required, fewer signal tracks... since you only need ONE address line, whereas before you needed address lines going to both chips.

4./ Lower power consumption.

win-win-win-win