Tuesday, March 7th 2017

AMD "Naples" is a 32-core Zen Based Monstrosity

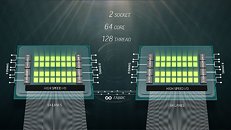

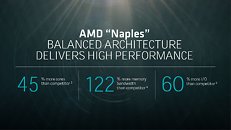

AMD today unveiled the "Naples" enterprise processor, and it is big. The chip could mark AMD's return to competitive enterprise CPUs after years. The first "Naples" based part has some staggering specifications - 32 CPU cores spread across eight CCX units, SMT enabling 64 threads, an octa-channel (yes, eight channels) DDR4 integrated memory controller, an industry-leading 64-lane PCI-Express gen 3.0 root complex, and AMD's new Infinity Fabric interconnect, which lets it talk to the neighboring CPU, in a 2P system. The IMC supports up to 2 TB of memory.

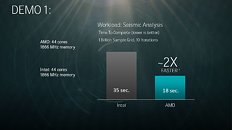

AMD will competitively price "Naples" against Intel's Xeon E5-2600 series 2P chips, offering more cores, wider memory interfaces, more memory support, and more PCIe lanes. AMD will tap into the good energy-efficiency of its "Zen" architecture to clock these chips competitively higher than Intel chips, to churn out more overall performance. AMD is scheduled to launch the first processors based on the "Naples" silicon, within Q2-2017."Today marks the first major milestone in AMD re-asserting its position as an innovator in the datacenter and returning choice to customers in high-performance server CPUs," said Forrest Norrod, senior vice president and general manager, Enterprise, Embedded and Semi-Custom business unit, AMD. "'Naples' represents a completely new approach to supporting the massive processing requirements of the modern datacenter. This groundbreaking system-on-chip delivers the unique high-performance features required to address highly virtualized environments, massive data sets and new, emerging workloads."

AMD will competitively price "Naples" against Intel's Xeon E5-2600 series 2P chips, offering more cores, wider memory interfaces, more memory support, and more PCIe lanes. AMD will tap into the good energy-efficiency of its "Zen" architecture to clock these chips competitively higher than Intel chips, to churn out more overall performance. AMD is scheduled to launch the first processors based on the "Naples" silicon, within Q2-2017."Today marks the first major milestone in AMD re-asserting its position as an innovator in the datacenter and returning choice to customers in high-performance server CPUs," said Forrest Norrod, senior vice president and general manager, Enterprise, Embedded and Semi-Custom business unit, AMD. "'Naples' represents a completely new approach to supporting the massive processing requirements of the modern datacenter. This groundbreaking system-on-chip delivers the unique high-performance features required to address highly virtualized environments, massive data sets and new, emerging workloads."

59 Comments on AMD "Naples" is a 32-core Zen Based Monstrosity

Not enough pins on the socket? To reduce PCB cost? To unlock them with the first speed bump update?

Due to the Zen core design, 12 cores will have 48 PCI-E Lanes, for each 4 cores you can add 16 pci-e Lanes.

Additional details:

I have no clue if R3 will have 16 lanes or 32 on die as the quadcores may be defective 8 cores or how they do that, 6 cores will be a 8 core with 1 core disabled in each CCX. and will retain L3 cache and PCI-e Lanes.

We may even see 2-3 core cpu'.

Also keep in mind usable PCI-E lanes is not the lanes the CPU has, regardless of AMD and or Intel.

USB3, Southbridges/fch (if present) consume 4-8 pci-e lanes

A 16 core monster for enthusiasts or prosumers and to mock Intels upcoming 12 core Extreme edition...

Btw, technically, this should be able to run Crysis. I mean, Windows 10 Pro 64bit supports 2 physical CPU's (and supposedly no real limits on the cores afaik), 512GB RAM and the board has PCIe slots to stick many graphic cards in it :D

There is also a matter of Intel platform being proven tech while Ryzen is unknown.

Not sure if it was ment too but that made me laugh!

AMD's PR game is strong.

However, outside of linux and cloud setups, I'm wondering how a 'all the cores' approach to the server market will serve AMD considering the 2016 license change to 2 Sockets, 8 cores a socket, anymore, pay more.

That being said, considering how AMD's SMT scales better than Intels HyperThreading, I am legitimately excited for this as a server product.

I am sorry, but when Intel sells a core it has an FPU and an integer core and when they sell me a quad channel memory controller it is an actual quad channel controller...No tricks no halfsies none of this AMD PR nonsense. This is why people do not trust their products.

Doing the maths to get two tbyte on a 2p server each channel needs to run 64Gb of memory.

As for 4p think of the pciex cost in interlinks there would be few if any left over.

Me and @Eidairman have discussed this in the past , it's unclear exactly what is connected through am4s pins to me at least ,is a 390x chipset possible with more pciex and more memory controller , I don't think we have the pins for quad channel myself but they could up the lanes or bandwidth available in later chips perhaps.

I only use a 8 threaded Intel chip so that's why I ask :confused: