TSMC 3nm Node to Make 20% of Company's Revenues in 2024

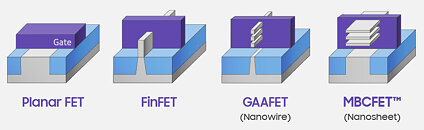

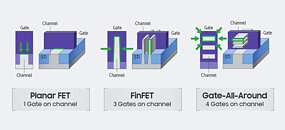

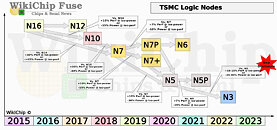

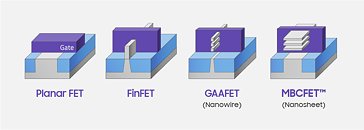

The 3 nm EUV node, which will be TSMC's final semiconductor fabrication node to implement FinFET transistors, will make for a staggering 20% of TSMC's revenues in 2024, a report by ICSmart says. 20% is big for a new foundry node, considering that TSMC is simultaneously running 4 nm and 5 nm EUV nodes; 6 nm and 7 nm DUV nodes; and several older mature nodes. Apple is expected to be the foundry's biggest customer for 3 nm, as it could power the company's current A17 and M3, and upcoming A18 and M4 line of chips for its next-generation iPhone and MacBooks; followed by NVIDIA, AMD, and possibly even Intel. AMD is expected to build some versions of its upcoming "Zen 5" processors on 3 nm; while Intel is expected to use 3 nm for some of the tiles of its upcoming "Lunar Lake" processor. The same report goes to suggest that 3 nm will make up 30% of TSMC's revenues in 2025.