2019 the Year of 1TB SSDs: Prices Fall by 50%

1-Terabyte SSDs could become a new mainstream-desktop must-have in 2019, as prices of the drives have fallen by 50 percent year-over-year, according to DigiTimes. A 1 TB SATA SSD in the 2.5-inch form-factor can now be had for as little as $99, while faster NVMe drives in the M.2 form-factor start around $130. At the beginning of 2018, 1 TB SATA SSDs used to start around the $160-mark, and NVMe drives north of $200. The 1 TB category includes 960 GB, 1000 GB, and 1024 GB marketed capacities with varying amounts of overprovisioning set by manufacturers.

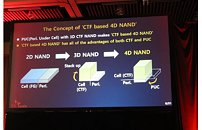

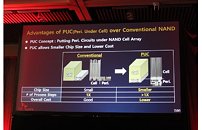

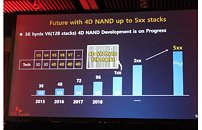

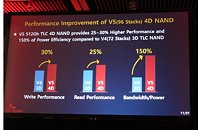

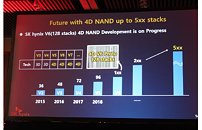

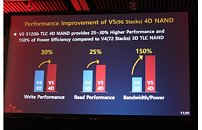

Falling SSD prices are accelerated by the entry of cost-effective 96-layer 3D NAND flash, higher-density QLC NAND flash, undigested inventories of drives based on older technologies such as 64-layer or TLC NAND flash; and a 15 percent sequential quarterly drop in NAND flash prices in the industry. Growth in speeds of client-segment SSDs have remained largely flat over the year, and not much is to be expected in performance growth other than perhaps the advent of PCIe gen 4.0 based enterprise SSDs towards the end of the year.

Falling SSD prices are accelerated by the entry of cost-effective 96-layer 3D NAND flash, higher-density QLC NAND flash, undigested inventories of drives based on older technologies such as 64-layer or TLC NAND flash; and a 15 percent sequential quarterly drop in NAND flash prices in the industry. Growth in speeds of client-segment SSDs have remained largely flat over the year, and not much is to be expected in performance growth other than perhaps the advent of PCIe gen 4.0 based enterprise SSDs towards the end of the year.