TSMC to Start 2 nm Production by 2025, 3 nm by the End of 2022

Responding to investor questions in TSMC's first quarter earnings call for 2022, CEO C. C. Wei reiterated that the company's upcoming manufacturing processes are generally moving smoothly throughout development. Even as TSMC announced historic revenues on the back of increased pricing throughout the semiconductor industry, the company is showing no signs of slowing down on its development. When further asked regarding the company's ability to navigate the world's troubled, inflation-ridden waters, Wei added that TSMC's strategic positioning as the leading semiconductor foundry makes it resilient to market and demand fluctuations.

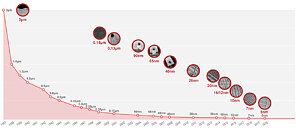

TSMC's roadmap has seen multiple accelerations of late, which have placed 3 nm tape-out to occur before the end of the year. Perhaps more significantly, the company's next-generation 2 nm manufacturing process, which will make use of GAA (Gate All Around) transistor designs for greater design efficiency and density, are still on track for a 2025 volume production following an expected 2024 tape-out.

TSMC's roadmap has seen multiple accelerations of late, which have placed 3 nm tape-out to occur before the end of the year. Perhaps more significantly, the company's next-generation 2 nm manufacturing process, which will make use of GAA (Gate All Around) transistor designs for greater design efficiency and density, are still on track for a 2025 volume production following an expected 2024 tape-out.