Huawei's Loss AMD's Gain, TSMC Develops Special 5nm Node

With Mainland Chinese tech giant Huawei being effectively cut off from contracting Taiwanese TSMC to manufacture its next-generation HiSilicon 5G mobile SoCs, and NVIDIA switching to Samsung for its next-generation GPUs, TSMC is looking to hold on to large high-volume customers besides Apple and Qualcomm, so as to not let them dictate pricing. AMD is at the receiving end of the newfound affection, with the semiconductor firm reportedly developing a new refinement of its 5 nm node specially for AMD, possibly to make Sunnyvale lock in on TSMC for its future chip architectures. A ChainNews report decoded by @chiakokhua sheds light on this development.

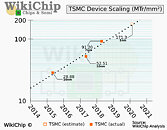

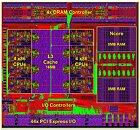

AMD is developing its "Zen 4" CPU microarchitecture for a 5 nm-class silicon fabrication node, although the company doesn't appear to have zeroed in on a node for its RDNA3 graphics architecture and CDNA2 scalar compute architecture. In its recent public reveal of the two, AMD chose not to specify the foundry node for the two, which come out roughly around the same time as "Zen 4." It wouldn't be far fetched to predict that AMD and TSMC were waiting on certainty for the new 5 nm-class node's development. There are no technical details of this new node. AMD's demand for TSMC is expected to be at least 20,000 12-inch wafers per month.

AMD is developing its "Zen 4" CPU microarchitecture for a 5 nm-class silicon fabrication node, although the company doesn't appear to have zeroed in on a node for its RDNA3 graphics architecture and CDNA2 scalar compute architecture. In its recent public reveal of the two, AMD chose not to specify the foundry node for the two, which come out roughly around the same time as "Zen 4." It wouldn't be far fetched to predict that AMD and TSMC were waiting on certainty for the new 5 nm-class node's development. There are no technical details of this new node. AMD's demand for TSMC is expected to be at least 20,000 12-inch wafers per month.