TheLostSwede

News Editor

- Joined

- Nov 11, 2004

- Messages

- 17,486 (2.40/day)

- Location

- Sweden

| System Name | Overlord Mk MLI |

|---|---|

| Processor | AMD Ryzen 7 7800X3D |

| Motherboard | Gigabyte X670E Aorus Master |

| Cooling | Noctua NH-D15 SE with offsets |

| Memory | 32GB Team T-Create Expert DDR5 6000 MHz @ CL30-34-34-68 |

| Video Card(s) | Gainward GeForce RTX 4080 Phantom GS |

| Storage | 1TB Solidigm P44 Pro, 2 TB Corsair MP600 Pro, 2TB Kingston KC3000 |

| Display(s) | Acer XV272K LVbmiipruzx 4K@160Hz |

| Case | Fractal Design Torrent Compact |

| Audio Device(s) | Corsair Virtuoso SE |

| Power Supply | be quiet! Pure Power 12 M 850 W |

| Mouse | Logitech G502 Lightspeed |

| Keyboard | Corsair K70 Max |

| Software | Windows 10 Pro |

| Benchmark Scores | https://valid.x86.fr/yfsd9w |

There has been a fair bit of confusion about AMD's upcoming AM5 platform when it comes to connectivity and we're going to break things down and explain what the difference is between the B650 and X670 boards. We're also going to cover the processor connectivity, since that's an integral part of any motherboard these days. All the information in this article is based on what we've been told by various sources during Computex.

Connectivity from the Processor

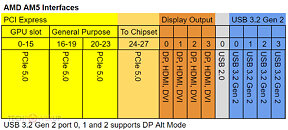

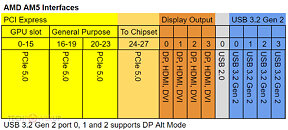

Starting with the Zen 4 processor's lanes, all of its PCIe lanes are PCIe 5.0 and there are a total of 28 lanes. The first 16 PCI Express lanes will be used for a single x16 PCIe slot, or they can be split into two x8 slots. AMD's requirements only enforce PCIe 5.0 on the X670E boards, which means PCIe 4.0 will be applicable to lower cost motherboards.

The new Zen 4 Ryzen processors will have eight general purpose lanes, of which at least four will be required to be dedicated to an M.2 storage slot (always Gen 5). The other four lanes are up to the motherboard manufacturers. Some boards will use these to implement Thunderbolt 4 (Intel Maple Ridge JHL8540) or USB4 (ASMedia ASM4242). If none of these options are used, these lanes can go towards an additional M.2 slot.

With integrated graphics becoming standard on Zen 4, the first generation of AM5 processors will offer four dedicated display outputs, with HDMI 2.1 and DisplayPort 2.0 being supported, but neither being required as far as we understand. There are also four USB 3.2 Gen 2 (10 Gbps) ports and at least one USB 2.0 port coming from the processor. Three of the USB 3.2 ports also support DP Alt Mode, something we've seen several announced boards supporting on at least one USB-C port. This seems to be up to the motherboard manufacturers to implement once again.

The remaining four PCIe lanes are used for connecting to the chipset. Just to clarify, on the processor side these do support PCI-Express 5.0, the chipset only supports PCIe 4.0, so the link negotiation mechanism will downgrade the link to Gen 4.

Chipset Connectivity

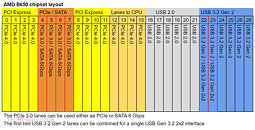

The way AMD presented their AM5 chipset options at Computex, it seemed that these each is an independent designs, based on its own silicon. In reality AMD has partnered with ASMedia to create a single chipset, called "Promontory 21," which is used in various configurations. For the X670 and X670E they are daisy-chaining a pair of B650 chipsets together, for additional connectivity options.

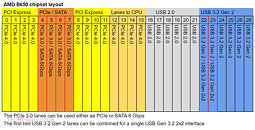

Promontory 21 offers a total of 16 PCI-Express lanes. Four of these are used to connect to the CPU, over a Gen 4 interface, as mentioned before. In the X670/X670E daisy-chained configuration the secondary chipset connects to the primary chipset, it has no direct link to the processor. This means that on the primary chipset another four lanes are used up, leaving eight usable PCIe lanes, whereas the secondary chipset has 12 usable PCIe lanes. Four of the lanes are PCIe 3.0, although these are muxed interfaces with SATA 6 Gbps. This allows the motherboard manufacturers to choose how they want to implement those interfaces and as we've seen, ASRock has gone for eight SATA ports, whereas most other board makers appear to be going for six on their X670 and X670E motherboards.

In other words, B650 motherboards will have a total of eight usable PCIe 4.0 lanes and four PCIe 3.0 or SATA 6 Gbps interfaces. X670 and X670E motherboards will have 12 PCIe 4.0 lanes and up to eight PCIe 3.0 or SATA 6 Gbps interfaces. In addition to this, each chipset will have six USB 3.2 Gen 2 (10 Gbps) interfaces, where the first two can be combined into a single USB 3.2 Gen 2x2 (20 Gbps) interface. This means X670 and X670E boards can have a total of 16 USB 3.2 Gen 2 (10 Gbps) ports, or two USB 3.2 Gen 2x2 (20 Gbps) ports and 12 USB 3.2 Gen 2 (10 Gbps) ports, including the USB 3.2 Gen 2 (10 Gbps) ports from the processor. Finally there's support for up to six USB 2.0 ports from the chipset. As a side note, any motherboard with more than two USB 3.2 Gen 2x2 (20 Gbps) ports, will be using a third party host controller or a hub.

Compared to Intel Alder Lake

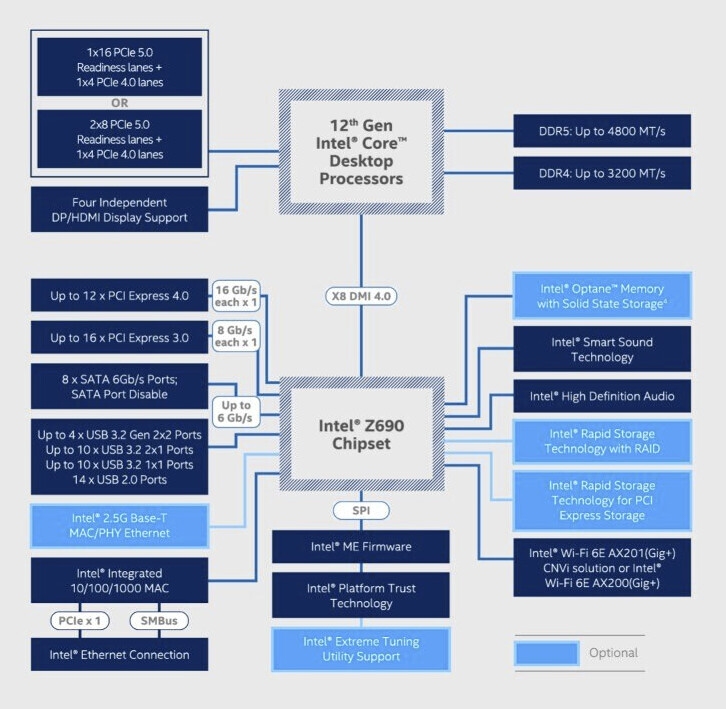

Compared to Intel's Z690 chipset, which has support for a total of 28 PCIe lanes, AMD has clearly decided to scale things back a little bit. In all fairness, Intel doesn't support more than 12 PCIe 4.0 lanes from the Z690 chipset and four of those lanes are shared with SATA 6 Gbps ports. Intel wins by having support for an additional 12 PCIe 3.0 lanes though, but two of those are shared with an Ethernet MAC, something AMD doesn't do, as the company relies on PCIe based Ethernet controllers. It's worth noting that Intel has a wider bus to some of its chipsets, as their CPUs support eight DMI 4.0 lanes. Comparing AMD's B650 chipset with Intel's B660, AMD comes out slightly ahead if high-speed interfaces matter, as the B660 chipset only supports six PCIe 4.0 lanes and eight PCIe 3.0 lanes, although none of its four SATA 6 Gbps ports are shared with PCIe.

The Z690 chipset supports a total of 10 USB 3.2 Gen 2 (10 Gbps) interfaces, but as with AMD, two interfaces are combined to create a single 20 Gbps interface, which means up to four USB 3.2 Gen 2x2 (20 Gbps) ports are supported. The B660 chipset supports two USB 3.2 Gen 2x2 (20 Gbps) plus two USB 3.2 Gen 1 (10 Gbps) ports, or six 10 Gbps ports. That said, Intel doesn't have any USB ports inside the CPU, which makes this something of a draw, depending on how the motherboard makers implement the connectivity options on their motherboards.

What we obviously don't know at this point is how much of a performance penalty there will be for AMD having two chipsets, especially when it comes to high-speed storage devices. We've seen some concerns about this implementation in virtualized environments and how these devices will appear to the OS in such a case, but we don't share those concerns. We expect the primary chipset to appear as PCIe bridge to the host system, a mechanism that is part of the specification and has been supported and used for many years. These are things we're going to have to wait and see how they play out, but AMD clearly deemed the tradeoffs reasonable enough versus the cost of developing multiple different chipsets.

View at TechPowerUp Main Site

Connectivity from the Processor

Starting with the Zen 4 processor's lanes, all of its PCIe lanes are PCIe 5.0 and there are a total of 28 lanes. The first 16 PCI Express lanes will be used for a single x16 PCIe slot, or they can be split into two x8 slots. AMD's requirements only enforce PCIe 5.0 on the X670E boards, which means PCIe 4.0 will be applicable to lower cost motherboards.

The new Zen 4 Ryzen processors will have eight general purpose lanes, of which at least four will be required to be dedicated to an M.2 storage slot (always Gen 5). The other four lanes are up to the motherboard manufacturers. Some boards will use these to implement Thunderbolt 4 (Intel Maple Ridge JHL8540) or USB4 (ASMedia ASM4242). If none of these options are used, these lanes can go towards an additional M.2 slot.

With integrated graphics becoming standard on Zen 4, the first generation of AM5 processors will offer four dedicated display outputs, with HDMI 2.1 and DisplayPort 2.0 being supported, but neither being required as far as we understand. There are also four USB 3.2 Gen 2 (10 Gbps) ports and at least one USB 2.0 port coming from the processor. Three of the USB 3.2 ports also support DP Alt Mode, something we've seen several announced boards supporting on at least one USB-C port. This seems to be up to the motherboard manufacturers to implement once again.

The remaining four PCIe lanes are used for connecting to the chipset. Just to clarify, on the processor side these do support PCI-Express 5.0, the chipset only supports PCIe 4.0, so the link negotiation mechanism will downgrade the link to Gen 4.

Chipset Connectivity

The way AMD presented their AM5 chipset options at Computex, it seemed that these each is an independent designs, based on its own silicon. In reality AMD has partnered with ASMedia to create a single chipset, called "Promontory 21," which is used in various configurations. For the X670 and X670E they are daisy-chaining a pair of B650 chipsets together, for additional connectivity options.

Promontory 21 offers a total of 16 PCI-Express lanes. Four of these are used to connect to the CPU, over a Gen 4 interface, as mentioned before. In the X670/X670E daisy-chained configuration the secondary chipset connects to the primary chipset, it has no direct link to the processor. This means that on the primary chipset another four lanes are used up, leaving eight usable PCIe lanes, whereas the secondary chipset has 12 usable PCIe lanes. Four of the lanes are PCIe 3.0, although these are muxed interfaces with SATA 6 Gbps. This allows the motherboard manufacturers to choose how they want to implement those interfaces and as we've seen, ASRock has gone for eight SATA ports, whereas most other board makers appear to be going for six on their X670 and X670E motherboards.

In other words, B650 motherboards will have a total of eight usable PCIe 4.0 lanes and four PCIe 3.0 or SATA 6 Gbps interfaces. X670 and X670E motherboards will have 12 PCIe 4.0 lanes and up to eight PCIe 3.0 or SATA 6 Gbps interfaces. In addition to this, each chipset will have six USB 3.2 Gen 2 (10 Gbps) interfaces, where the first two can be combined into a single USB 3.2 Gen 2x2 (20 Gbps) interface. This means X670 and X670E boards can have a total of 16 USB 3.2 Gen 2 (10 Gbps) ports, or two USB 3.2 Gen 2x2 (20 Gbps) ports and 12 USB 3.2 Gen 2 (10 Gbps) ports, including the USB 3.2 Gen 2 (10 Gbps) ports from the processor. Finally there's support for up to six USB 2.0 ports from the chipset. As a side note, any motherboard with more than two USB 3.2 Gen 2x2 (20 Gbps) ports, will be using a third party host controller or a hub.

Compared to Intel Alder Lake

Compared to Intel's Z690 chipset, which has support for a total of 28 PCIe lanes, AMD has clearly decided to scale things back a little bit. In all fairness, Intel doesn't support more than 12 PCIe 4.0 lanes from the Z690 chipset and four of those lanes are shared with SATA 6 Gbps ports. Intel wins by having support for an additional 12 PCIe 3.0 lanes though, but two of those are shared with an Ethernet MAC, something AMD doesn't do, as the company relies on PCIe based Ethernet controllers. It's worth noting that Intel has a wider bus to some of its chipsets, as their CPUs support eight DMI 4.0 lanes. Comparing AMD's B650 chipset with Intel's B660, AMD comes out slightly ahead if high-speed interfaces matter, as the B660 chipset only supports six PCIe 4.0 lanes and eight PCIe 3.0 lanes, although none of its four SATA 6 Gbps ports are shared with PCIe.

The Z690 chipset supports a total of 10 USB 3.2 Gen 2 (10 Gbps) interfaces, but as with AMD, two interfaces are combined to create a single 20 Gbps interface, which means up to four USB 3.2 Gen 2x2 (20 Gbps) ports are supported. The B660 chipset supports two USB 3.2 Gen 2x2 (20 Gbps) plus two USB 3.2 Gen 1 (10 Gbps) ports, or six 10 Gbps ports. That said, Intel doesn't have any USB ports inside the CPU, which makes this something of a draw, depending on how the motherboard makers implement the connectivity options on their motherboards.

What we obviously don't know at this point is how much of a performance penalty there will be for AMD having two chipsets, especially when it comes to high-speed storage devices. We've seen some concerns about this implementation in virtualized environments and how these devices will appear to the OS in such a case, but we don't share those concerns. We expect the primary chipset to appear as PCIe bridge to the host system, a mechanism that is part of the specification and has been supported and used for many years. These are things we're going to have to wait and see how they play out, but AMD clearly deemed the tradeoffs reasonable enough versus the cost of developing multiple different chipsets.

View at TechPowerUp Main Site