- Joined

- Oct 9, 2007

- Messages

- 47,670 (7.43/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

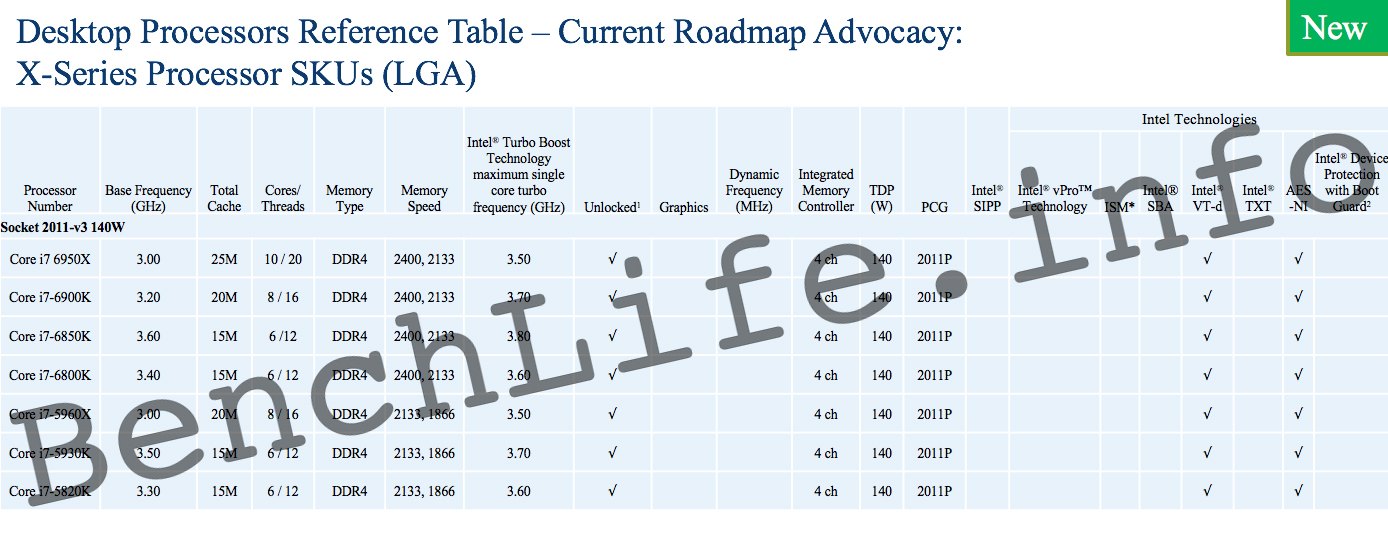

Intel is breaking away from its tradition of three Core i7 HEDT (high-end desktop) processors per generation, capturing price points of $400, $600, and $1000; with its upcoming Core i7 "Broadwell-E" HEDT lineup. According to leaked documents accessed by BenchLife.info, the company is readying four SKUs based on the 14 nm "Broadwell-E" silicon, these include the Core i7-6800K, the Core i7-6850K, the Core i7-6900K, and the Core i7-6950X.

The Core i7-6800K and i7-6850K are six-core chips, with HyperThreading enabling 12 logical CPUs, and 15 MB shared L3 cache. The i7-6800K is clocked at 3.40 GHz, with a 3.60 GHz Turbo Boost frequency. The i7-6850K is a notch above, with 3.60 GHz core, and 3.80 GHz Turbo Boost frequency. The slide doesn't mention if either of the two parts feature a limited PCIe root complex, like the one on the i7-5820K.

As we move up the lineup, there's the Core i7-6900K. This is an eight-core chip, with HyperThreading enabling 16 logical CPUs, and with 20 MB L3 cache at its disposal. Its core is clocked at 3.20 GHz, with a rather healthy 3.70 GHz Turbo Boost. At the very top of the lineup, is the Core i7-6950X. Intel's first consumer 10-core chip, with HyperThreading giving your OS a whopping 20 logical CPUs to deal with, this chip features 25 MB L3 cache, and is clocked at 3.00 GHz, with 3.50 GHz Turbo Boost.

All four chips in the lineup feature 140W TDP, unlocked base-clock multipliers, and will be compatible with existing socket LGA2011v3 motherboards with firmware updates. The low clock speeds on some of these chips right off the bat, could be Intel's way of not letting the rated TDP be higher than 140W. With the right cooling, the target consumers of these chips could overclock these chips.

Intel is planning to launch these Core i7 "Broadwell-E" chips in the second quarter of 2016.

View at TechPowerUp Main Site

The Core i7-6800K and i7-6850K are six-core chips, with HyperThreading enabling 12 logical CPUs, and 15 MB shared L3 cache. The i7-6800K is clocked at 3.40 GHz, with a 3.60 GHz Turbo Boost frequency. The i7-6850K is a notch above, with 3.60 GHz core, and 3.80 GHz Turbo Boost frequency. The slide doesn't mention if either of the two parts feature a limited PCIe root complex, like the one on the i7-5820K.

As we move up the lineup, there's the Core i7-6900K. This is an eight-core chip, with HyperThreading enabling 16 logical CPUs, and with 20 MB L3 cache at its disposal. Its core is clocked at 3.20 GHz, with a rather healthy 3.70 GHz Turbo Boost. At the very top of the lineup, is the Core i7-6950X. Intel's first consumer 10-core chip, with HyperThreading giving your OS a whopping 20 logical CPUs to deal with, this chip features 25 MB L3 cache, and is clocked at 3.00 GHz, with 3.50 GHz Turbo Boost.

All four chips in the lineup feature 140W TDP, unlocked base-clock multipliers, and will be compatible with existing socket LGA2011v3 motherboards with firmware updates. The low clock speeds on some of these chips right off the bat, could be Intel's way of not letting the rated TDP be higher than 140W. With the right cooling, the target consumers of these chips could overclock these chips.

Intel is planning to launch these Core i7 "Broadwell-E" chips in the second quarter of 2016.

View at TechPowerUp Main Site