- Joined

- Oct 9, 2007

- Messages

- 47,857 (7.38/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

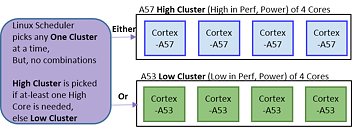

big.LITTLE is an innovation by ARM, which seeks to minimize power-draw on mobile devices. It is a sort of heterogeneous multi-core CPU design, in which a few "big" high-performance CPU cores work alongside a few extremely low-power "little" CPU cores. The idea here is that the low-power cores consume much lesser power at max load, than the high-performance cores at their minimum power-state, so the high-performance cores can be power-gated when the system doesn't need them (i.e. most of the time).

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.

Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

View at TechPowerUp Main Site

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.

Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

View at TechPowerUp Main Site