- Joined

- Jul 5, 2013

- Messages

- 31,654 (7.23/day)

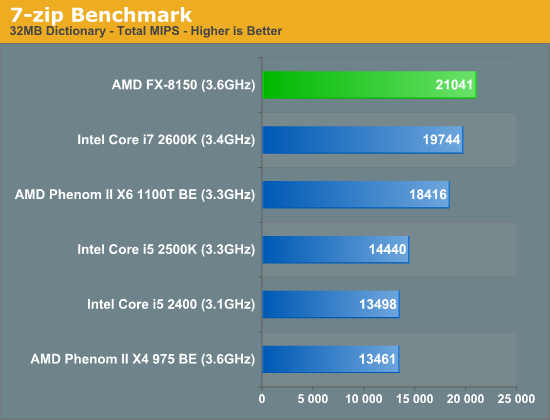

And we all know people like that.Then you have the group of people that think an Intel i7 chip has 7 cores, the i5 has 5 cores and so on. They might know a little more about computers than your grandma, but they don't really know all that much...

And this is only their own responsibility. Not AMD's fault. Regardless of the number of cores, performance is always the more telling point. Reviews will always tell a potential buyer what they're getting into. There is no excuse for buying something like the CPU's in question and whining later about performance or whether or not the claimed 8 cores are actually 8 cores.but then, they probably didn't research their product all that well, or read very many reviews, or maybe not even understand computer hardware quite so well in general

Only whether or not there is a claim about false advertising, which the plaintiffs will have to make a case for and they have a serious uphill battle.What do you mean? If they advertise the choice they made as one they did not, court pretty clearly has authority to say something about it.