- Joined

- Oct 9, 2007

- Messages

- 47,895 (7.38/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

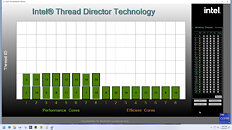

Intel in its Architecture Day presentation Thread Director, a hardware component present on the "Alder Lake" silicon, which makes the Hybrid architecture of the processor work flawlessly. "Alder Lake-S" is the first desktop processor with two kinds of x86 CPU cores—the larger Performance P-cores, and the smaller Efficient E-cores, which work in a setup not unlike big.LITTLE by Arm.

The x86-based "Alder Lake" processor has a much more complex ISA, and the E-cores don't have all of the instruction sets or hardware capabilities that the P-cores do. The two cores operate at very different performance/Watt bands, and are optimized for vastly different workloads. At the same time, sending a workload to the wrong kind of core could not only impact performance, but also crash, due to an ISA mismatch. Intel realized that it will take a lot more than mere OS-level awareness to solve the problem, and so innovated the Thread Director.

Put simply, Intel Thread Director is a highly specialized hardware abstraction layer (HAL) that interfaces with the operating system and software on one side; and the two groups of CPU cores, on the other. Its job is to analyze a workload, distribute it among the P-core or E-core clusters, at a granular level (i.e. thread-level). If specific threads of an application don't invoke certain kinds of instructions and are determined to be low-priority, they're dispatched to the E-core cluster. Threads that lose priority are parked onto the E-cores from the P-cores, too.

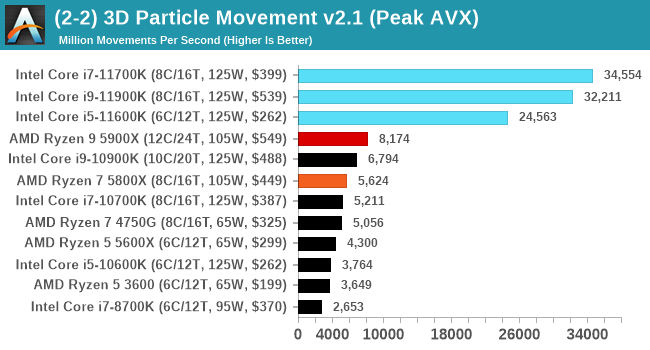

The P-cores get priority when a thread requires instructions exclusive to P-cores (such as AVX-512 or DLBoost). Thread Director also works with the OS kernel to discern background tasks from foreground/priority ones. This probably works with a software-side component that's included with the Chipset INF software, if not an exclusive driver. Thread Director ensures that lightweight or low-priority tasks don't needlessly invoke P-cores, and when the system is idling, the processor's power management can probably gate power to P-cores for major power savings (this is assuming Alder Lake features a power-gating technology similar to "Lakefield.").

Intel will recommend Windows 11 as the most optimal OS for "Alder Lake," as it meets Thread Director half way with OS Scheduler awareness of hybrid processor architectures. It remains to be seen, however, whether Thread Director requires this.

View at TechPowerUp Main Site

The x86-based "Alder Lake" processor has a much more complex ISA, and the E-cores don't have all of the instruction sets or hardware capabilities that the P-cores do. The two cores operate at very different performance/Watt bands, and are optimized for vastly different workloads. At the same time, sending a workload to the wrong kind of core could not only impact performance, but also crash, due to an ISA mismatch. Intel realized that it will take a lot more than mere OS-level awareness to solve the problem, and so innovated the Thread Director.

Put simply, Intel Thread Director is a highly specialized hardware abstraction layer (HAL) that interfaces with the operating system and software on one side; and the two groups of CPU cores, on the other. Its job is to analyze a workload, distribute it among the P-core or E-core clusters, at a granular level (i.e. thread-level). If specific threads of an application don't invoke certain kinds of instructions and are determined to be low-priority, they're dispatched to the E-core cluster. Threads that lose priority are parked onto the E-cores from the P-cores, too.

The P-cores get priority when a thread requires instructions exclusive to P-cores (such as AVX-512 or DLBoost). Thread Director also works with the OS kernel to discern background tasks from foreground/priority ones. This probably works with a software-side component that's included with the Chipset INF software, if not an exclusive driver. Thread Director ensures that lightweight or low-priority tasks don't needlessly invoke P-cores, and when the system is idling, the processor's power management can probably gate power to P-cores for major power savings (this is assuming Alder Lake features a power-gating technology similar to "Lakefield.").

Intel will recommend Windows 11 as the most optimal OS for "Alder Lake," as it meets Thread Director half way with OS Scheduler awareness of hybrid processor architectures. It remains to be seen, however, whether Thread Director requires this.

View at TechPowerUp Main Site