- Joined

- Oct 9, 2007

- Messages

- 47,886 (7.38/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

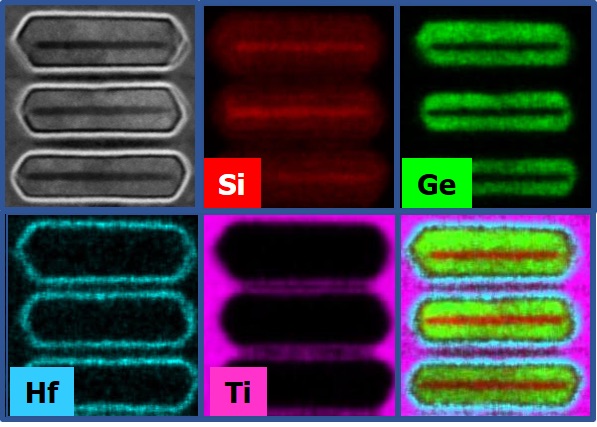

TSMC will commercialize its N3 (3 nm) EUV silicon fabrication node in 2022, with volume production set to commence in the second half of the year. The company is looking to maximize capacity on its current N5 (5 nm) node, which already serves major customers such as Apple. AMD is expected to utilize N5 allocation going into 2022 as its next-generation "Zen 4" processors are expected to leverage the node to drive up CPU core counts and caches. The company is also utilizing N6 (6 nm) for its CDNA2 compute accelerator logic dies. N5 could also power mobile application processors from several manufacturers.

View at TechPowerUp Main Site

View at TechPowerUp Main Site