- Joined

- Oct 9, 2007

- Messages

- 47,695 (7.42/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

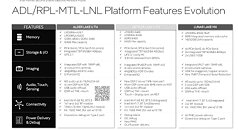

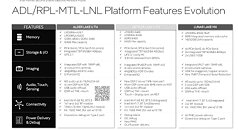

With the reality of high performance Arm processors from Apple and Qualcomm threatening Intel's market share in the client computing space, Intel is working on learner more PCB-efficient client SoCs that can take the fight to them, while holding onto the foundations of x86. The first such form-factor of processors are dubbed -MX. These are essentially -U segment processors with memory on package, to minimize PCB footprint. Intel has fully integrated the PCH into the processor chip with "Meteor Lake," with PCH functions scattered across the SoC and I/O tiles of the processor. An SoC package with dimensions similar to those of -UP4 packages meant for ultrabooks, can now cram main memory, so the PCBs of next-generation notebooks can be further compacted.

Intel had recently shown Meteor Lake-MX packages to the press as a packaging technology demonstration in its Arizona facility. It's unclear whether this could release as actual products, but in a leaked company presentation, confirmed that its first commercial outing will be with Lunar Lake-MX. The current "Alder Lake-UP4" package measures 19 mm x 28.5 mm, and is a classic multi-chip module that combines a monolithic "Alder Lake" SoC die with a PCH die. The "Meteor Lake-UP4" package measures 19 mm x 23 mm, and is a chiplet-based processor, with a Foveros base tile that holds the Compute (CPU cores), Graphics (iGPU), SoC and I/O (platform core-logic) tiles. The "Lunar Lake-MX" package is slightly larger than its -UP4 predecessors, measuring 27 mm x 27.5 mm, but completely frees up space on the PCB for memory.

The "Lunar Lake-MX" package features a Foveros base tile, just like "Meteor Lake-UP4," but with two LPDDR5X memory chips on package. Depending on the processor model, the memory sizes on offer will be either 16 GB or 32 GB, across a 160-bit dual-channel (4x sub-channel) interface. Memory speeds on offer will be as high as LP5X-8533. Intel is innovating what it calls a "memory side cache," which is an 8 MB fast SRAM cache located somewhere along the memory I/O.

The "Lunar Lake" microarchitecture is expected to see Intel reorganize the various components of the SoC across the tiles. There is expected to be one large logic-heavy tile called the "CPU tile," and a smaller platform core-logic heavy tile called the "SoC tile." With Lunar Lake, Intel Foundry Services (IFS) is expected to debut the company Intel 18A foundry node, which offers transistor densities and power/thermal characteristics comparable to 2 nm-class nodes by TSMC. From the looks of it, the entire CPU tile will be built on the TSMC N3B (3 nm) foundry node.

The CPU tile contains the compute complex along the high bandwidth North Fabric. The key components here are the Performance Compute cores, the Low-Power core clusters; the next-generation NPU which accelerates AI, the iGPU based on the Xe2 "Battlemage" graphics architecture, and the LPDDR5X memory controllers. There are other minor bandwidth-hungry components, such as the IPU (image processing), and media engine (video accelerators). The SoC die is now back to being a glorified PCH, with the various platform interfaces, PCIe, USB, and Thunderbolt I/O.

The compute muscle of "Lunar Lake-MX" will see a CPU with a 4P+4E configuration, with a very high degree of interoperability integration with the OS. The performance cores (P-cores) are codenamed "Lion Cove," and will be three generations ahead of the current "Raptor Cove," which means three consecutive cycles of IPC uplifts. The efficiency cores (E-cores) are codenamed "Skymont" and will be two generations ahead of the current "Gracemont." The upcoming "Crestmont" E-core architecture will be deployed on "Meteor Lake" and "Arrow Lake."

The graphics muscle is care of the Xe²-LPG graphics architecture, which draws from Intel's next-generation gaming graphics architecture codenamed "Battlemage." The iGPU on the "Lunar Lake-MX" package has 8 Xe cores worth 64 16-wide vector engines, full DirectX 12 Ultimate API feature-set, and hardware support for Intel's next systolic AI superscaling technology.

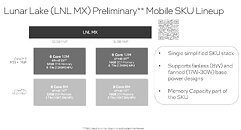

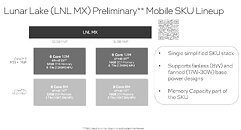

We are still far away from actual processor model numbers and SKUs, but Intel has drawn up some draft SKU segmentation for "Lunar Lake-MX." It sees 32 GB and 16 GB variants of Core 7 SKUs with 4P+4E CPUs and 8 Xe cores; and 32 GB and 16 GB variants of Core 5 SKUs with 4P+4E CPUs, and 7 Xe cores. Intel is targeting power envelopes as low as 8 W, for completely fanless devices, going all the way up to 30 W for high performance variants. The company aims for "Lunar Lake-MX" to compete in the same device category as the 2025 successors of Apple M3.

View at TechPowerUp Main Site | Source

Intel had recently shown Meteor Lake-MX packages to the press as a packaging technology demonstration in its Arizona facility. It's unclear whether this could release as actual products, but in a leaked company presentation, confirmed that its first commercial outing will be with Lunar Lake-MX. The current "Alder Lake-UP4" package measures 19 mm x 28.5 mm, and is a classic multi-chip module that combines a monolithic "Alder Lake" SoC die with a PCH die. The "Meteor Lake-UP4" package measures 19 mm x 23 mm, and is a chiplet-based processor, with a Foveros base tile that holds the Compute (CPU cores), Graphics (iGPU), SoC and I/O (platform core-logic) tiles. The "Lunar Lake-MX" package is slightly larger than its -UP4 predecessors, measuring 27 mm x 27.5 mm, but completely frees up space on the PCB for memory.

The "Lunar Lake-MX" package features a Foveros base tile, just like "Meteor Lake-UP4," but with two LPDDR5X memory chips on package. Depending on the processor model, the memory sizes on offer will be either 16 GB or 32 GB, across a 160-bit dual-channel (4x sub-channel) interface. Memory speeds on offer will be as high as LP5X-8533. Intel is innovating what it calls a "memory side cache," which is an 8 MB fast SRAM cache located somewhere along the memory I/O.

The "Lunar Lake" microarchitecture is expected to see Intel reorganize the various components of the SoC across the tiles. There is expected to be one large logic-heavy tile called the "CPU tile," and a smaller platform core-logic heavy tile called the "SoC tile." With Lunar Lake, Intel Foundry Services (IFS) is expected to debut the company Intel 18A foundry node, which offers transistor densities and power/thermal characteristics comparable to 2 nm-class nodes by TSMC. From the looks of it, the entire CPU tile will be built on the TSMC N3B (3 nm) foundry node.

The CPU tile contains the compute complex along the high bandwidth North Fabric. The key components here are the Performance Compute cores, the Low-Power core clusters; the next-generation NPU which accelerates AI, the iGPU based on the Xe2 "Battlemage" graphics architecture, and the LPDDR5X memory controllers. There are other minor bandwidth-hungry components, such as the IPU (image processing), and media engine (video accelerators). The SoC die is now back to being a glorified PCH, with the various platform interfaces, PCIe, USB, and Thunderbolt I/O.

The compute muscle of "Lunar Lake-MX" will see a CPU with a 4P+4E configuration, with a very high degree of interoperability integration with the OS. The performance cores (P-cores) are codenamed "Lion Cove," and will be three generations ahead of the current "Raptor Cove," which means three consecutive cycles of IPC uplifts. The efficiency cores (E-cores) are codenamed "Skymont" and will be two generations ahead of the current "Gracemont." The upcoming "Crestmont" E-core architecture will be deployed on "Meteor Lake" and "Arrow Lake."

The graphics muscle is care of the Xe²-LPG graphics architecture, which draws from Intel's next-generation gaming graphics architecture codenamed "Battlemage." The iGPU on the "Lunar Lake-MX" package has 8 Xe cores worth 64 16-wide vector engines, full DirectX 12 Ultimate API feature-set, and hardware support for Intel's next systolic AI superscaling technology.

We are still far away from actual processor model numbers and SKUs, but Intel has drawn up some draft SKU segmentation for "Lunar Lake-MX." It sees 32 GB and 16 GB variants of Core 7 SKUs with 4P+4E CPUs and 8 Xe cores; and 32 GB and 16 GB variants of Core 5 SKUs with 4P+4E CPUs, and 7 Xe cores. Intel is targeting power envelopes as low as 8 W, for completely fanless devices, going all the way up to 30 W for high performance variants. The company aims for "Lunar Lake-MX" to compete in the same device category as the 2025 successors of Apple M3.

View at TechPowerUp Main Site | Source

I'd like the source of that nonsense.

I'd like the source of that nonsense.