I doubt they would make them cheaper just because they are small and generally uselessAs long as it stays small in proportion I'll be happy. I'm glad AMD doesn't waste the die space. A 2D blitter is all that's needed for window compositing.

-

Welcome to TechPowerUp Forums, Guest! Please check out our forum guidelines for info related to our community.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD Sampling Next-Gen Ryzen Desktop "Medusa Ridge," Sees Incremental IPC Upgrade, New cIOD

- Thread starter btarunr

- Start date

Making the GPU bigger does increase the price though. That's already been clearly demonstrated with the MAX 300 range, aka Strix Halo. They're basically exactly what you've requested - A full blown chiplet set with a bloated I/O die containing a 8060 class GPU.

As I first stated, those sorts of APU packages will come along later.

As I first stated, those sorts of APU packages will come along later.

Last edited:

- Joined

- Apr 18, 2019

- Messages

- 2,991 (1.31/day)

- Location

- PNW, USA

| System Name | Metalia |

|---|---|

| Processor | AMD Ryzen 7 5800X3D |

| Motherboard | Asus TuF Gaming X570-PLUS |

| Cooling | ID Cooling 280mm AIO w/ Arctic P14s |

| Memory | 2x32GB DDR4-3600 |

| Video Card(s) | Sapphire Pulse RX 9070 XT |

| Storage | Optane P5801X 400GB, Samsung 990Pro 2TB |

| Display(s) | LG 32GS95UV 32" OLED 240/480hz 4K/1080P Dual Mode |

| Case | Geometric Future M8 Dharma |

| Audio Device(s) | Xonar Essence STX |

| Power Supply | Seasonic Focus GX-1000 Gold |

| Mouse | Attack Shark R3 Magnesium - White |

| Keyboard | Keychron K8 Pro - White - Tactile Brown Switch |

| Software | Windows 10 IoT Enterprise LTSC 2021 |

I've gathered the dual memory controllers are for "single channel, per controller" operation but, could this lay the foundation for 'not-quad channel' (in the same vein of DDR5's 'not-ECC')?

Basically, I'm thinking:

Each memory controller might not be 'fully loaded' with only 1 DIMM attached, and 2DIMMs per controller provides more bandwidth.

Basically, I'm thinking:

Each memory controller might not be 'fully loaded' with only 1 DIMM attached, and 2DIMMs per controller provides more bandwidth.

Strix point is a monolithic die that is also wired for gddr, normal ryzen chips have the igpu on the io die which is tiny and just quadrupling the number of CU on that isn’t going to make it all that much biggerMaking the GPU bigger does increase the price though. That's already been clearly demonstrated with the MAX 300 range, aka Strix Halo. They're basically exactly what you've requested - A full blown chiplet set with a bloated I/O die containing a 8060 class GPU.

As I first stated, those sorts of APU packages will come along later.

As long as it stays small in proportion I'll be happy. In other words, it stays insignificant and not worth any conversation. Leave the GPU beefing up to the APUs.

Zen6 changes that to be two 64-bit wide independent controllers that feeds two requests at a time. Presumably it'll still have the ability to fill single requests at double the rate.

In theory, for AM5 only, the controller count could be doubled again to 4 x 32-bit wide. This would then match the number of physical channels.

It looks like it had always been a single controller, on the AM4/AM5 platforms, that managed multiple channels. To always effect 128-bit wide operation, filling one request at a time.I've gathered the dual memory controllers are for "single channel, per controller" operation but, could this lay the foundation for 'not-quad channel' (in the same vein of DDR5's 'not-ECC')?

Basically, I'm thinking:

Each memory controller might not be 'fully loaded' with only 1 DIMM attached, and 2DIMMs per controller provides more bandwidth.

Zen6 changes that to be two 64-bit wide independent controllers that feeds two requests at a time. Presumably it'll still have the ability to fill single requests at double the rate.

In theory, for AM5 only, the controller count could be doubled again to 4 x 32-bit wide. This would then match the number of physical channels.

Last edited:

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

Strix Point can not use GDDR. Funnily they probably could add a GDDR7 memory controller if they got rid of the useless NPU which is a literal waste of sand.Strix point is a monolithic die that is also wired for gddr, normal ryzen chips have the igpu on the io die which is tiny and just quadrupling the number of CU on that isn’t going to make it all that much bigger

Could have sworn it used gddr, but yes it’s lpddr5 they surrounded the Soc with like they do a gpu with gddrStrix Point can not use GDDR. Funnily they probably could add a GDDR7 memory controller if they got rid of the useless NPU which is a literal waste of sand.

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

That's true, but your post just make me think that a GDDR APU would rock.Could have sworn it used gddr, but yes it’s lpddr5 they surrounded the Soc with like they do a gpu with gddr

- Joined

- Apr 18, 2019

- Messages

- 2,991 (1.31/day)

- Location

- PNW, USA

| System Name | Metalia |

|---|---|

| Processor | AMD Ryzen 7 5800X3D |

| Motherboard | Asus TuF Gaming X570-PLUS |

| Cooling | ID Cooling 280mm AIO w/ Arctic P14s |

| Memory | 2x32GB DDR4-3600 |

| Video Card(s) | Sapphire Pulse RX 9070 XT |

| Storage | Optane P5801X 400GB, Samsung 990Pro 2TB |

| Display(s) | LG 32GS95UV 32" OLED 240/480hz 4K/1080P Dual Mode |

| Case | Geometric Future M8 Dharma |

| Audio Device(s) | Xonar Essence STX |

| Power Supply | Seasonic Focus GX-1000 Gold |

| Mouse | Attack Shark R3 Magnesium - White |

| Keyboard | Keychron K8 Pro - White - Tactile Brown Switch |

| Software | Windows 10 IoT Enterprise LTSC 2021 |

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

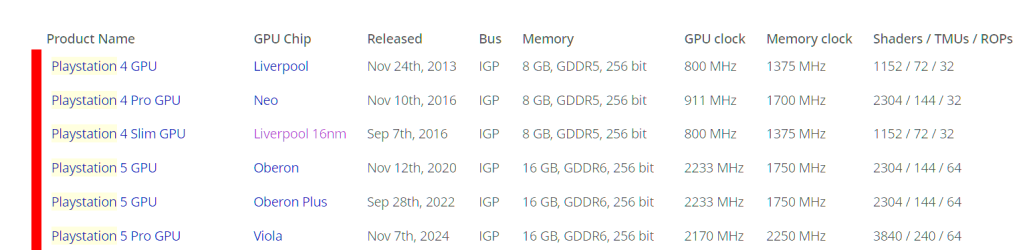

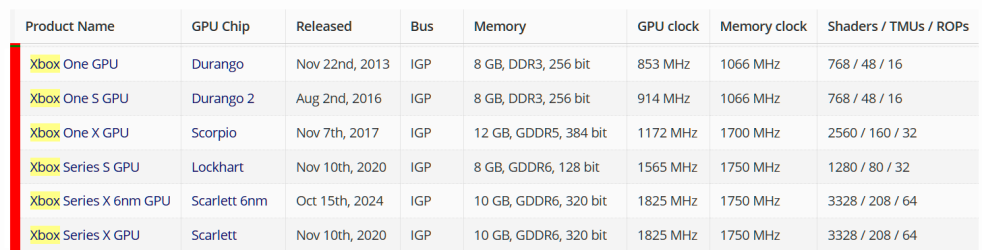

Exactly, that's what I meant. Even GDDR isn't too expensiveSony's and MSFT's Game Consoles, would indicate that they do indeed rock (vs. DDR System Memory sharing).

View attachment 407614View attachment 407615

- Joined

- Sep 1, 2020

- Messages

- 2,735 (1.54/day)

- Location

- Bulgaria

The latest rumor. Not just N2, but N2P for desktop, server and high level mobile parts logic chiplets. For Zen 6.

- Joined

- Jan 28, 2020

- Messages

- 4,823 (2.42/day)

Does Zen 6 need N2P ? Probably no.

The outcome will be a very small chiplet, around 30-35 sq. mm, with extremely high thermal density, very high temperatures, very thick IHS, and very unpleasant for the users to deal with.

When will AMD focus on the graphics parts where the real money is ?

The outcome will be a very small chiplet, around 30-35 sq. mm, with extremely high thermal density, very high temperatures, very thick IHS, and very unpleasant for the users to deal with.

When will AMD focus on the graphics parts where the real money is ?

- Joined

- Jan 14, 2023

- Messages

- 939 (1.03/day)

| System Name | Lenovo slim 5 16' |

|---|---|

| Processor | AMD 8845hs |

| Motherboard | Lenovo motherboard |

| Cooling | 2 fans |

| Memory | 64gb 5600mhz cl40 |

| Video Card(s) | 4070 laptop |

| Storage | 16tb, x2 8tb SSD |

| Display(s) | 16in 16:10 (1920x1200) 144hz |

| Power Supply | 230w psu |

i dont know of any mobile 12core CCD.Why limit yourself? Mobile Ryzen has 12 core CCDs.

Also, please learn what an E core is, and what a ryzen C core is. These are not the same thing.

CAMM2 modules are having the same signal integrity issues that DIMM modules have trying to push past 6000 mhz.

It'd be a lot easier to simply put a x3d cache on their APUs instead of another memory controller. Not to mention that a triple bus system is going to be significantly more expensive for the end consumer than a dual pus system like we have now.

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

They probably the 2 CCX on Strix Point. Its wrong but I get how one would make that mistake.i dont know of any mobile 12core CCD.

- Joined

- Dec 14, 2011

- Messages

- 1,491 (0.30/day)

- Location

- South-Africa

| Processor | AMD Ryzen 9 5900X |

|---|---|

| Motherboard | ASUS ROG STRIX B550-F GAMING (WI-FI) |

| Cooling | Noctua NH-D15 G2 |

| Memory | 32GB G.Skill DDR4 3600Mhz CL18 |

| Video Card(s) | ASUS RTX 5070Ti OC TUF |

| Storage | SAMSUNG 990 PRO 2TB |

| Display(s) | Dell S3220DGF |

| Case | Corsair iCUE 4000X |

| Audio Device(s) | ASUS Xonar D2X |

| Power Supply | Corsair AX760 Platinum |

| Mouse | Razer DeathAdder V2 - Wireless |

| Keyboard | Corsair K70 PRO - OPX Linear Switches |

| Software | Microsoft Windows 11 - Enterprise (64-bit) |

Here we go again...

Tell us what desktop applications need dozens of cores other than video encoding by the CPU?

Tell us why Intel thought it was okay to keep us on 4 Core / 8 Thread CPUs when the market screams for more? People don't just use do 1 thing at a time today, I want to game, I want to render, I want to browse, I want a movie in the background and I want to do it all at once without one affecting the other.

Anyways, looking forward to seeing what a Zen 6 12-Core X3D chip can do, 7Ghz with an IPC uplift? Yes please, I was excited for the 9800X3D, but I held off, I knew the upcoming one will be a beast, good things happen in 3. At the same time, I think for the first time, they will probably have to launch a new socket, hopefully not, but likely.

- Joined

- Jun 14, 2020

- Messages

- 5,810 (3.13/day)

| System Name | Mean machine |

|---|---|

| Processor | AMD 6900HS |

| Memory | 2x16 GB 4800C40 |

| Video Card(s) | AMD Radeon 6700S |

Intel had 6 core chips for 379$ since 2014 my man.Tell us why Intel thought it was okay to keep us on 4 Core / 8 Thread CPUs when the market screams for more?

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

Oh really? That means with how much the 9600X costs a 6-core hasn't really dropped in price.Intel had 6 core chips for 379$ since 2014 my man.

The only 6 core that Intel sold in 2014 was the $600 i7 4930K, which would be $800 today. Competition from AMD is a good thing or we'd probably still be stuck on quad cores unless buying a ridiculously expensive HEDT system. CPU's have gotten faster and cheaper.

- Joined

- Jun 19, 2024

- Messages

- 937 (2.38/day)

| System Name | XPS, Lenovo and HP Laptops, HP Xeon Mobile Workstation, HP Servers, Dell Desktops |

|---|---|

| Processor | Everything from Turion to 13900kf |

| Motherboard | MSI - they own the OEM market |

| Cooling | Air on laptops, lots of air on servers, AIO on desktops |

| Memory | I think one of the laptops is 2GB, to 64GB on gamer, to 128GB on ZFS Filer |

| Video Card(s) | A pile up to my knee, with a RTX 4090 teetering on top |

| Storage | Rust in the closet, solid state everywhere else |

| Display(s) | Laptop crap, LG UltraGear of various vintages |

| Case | OEM and a 42U rack |

| Audio Device(s) | Headphones |

| Power Supply | Whole home UPS w/Generac Standby Generator |

| Software | ZFS, UniFi Network Application, Entra, AWS IoT Core, Splunk |

| Benchmark Scores | 1.21 GigaBungholioMarks |

JFC man get your facts straight. 5820K. Just three minutes is all it takes for your posts to not be ignorant.The only 6 core that Intel sold in 2014 was the $600 i7 4930K, which would be $800 today. Competition from AMD is a good thing or we'd probably still be stuck on quad cores unless buying a ridiculously expensive HEDT system. CPU's have gotten faster and cheaper.

Intel® Core™ i7-5820K Processor (15M Cache, up to 3.60 GHz) - Product Specifications | Intel

Intel® Core™ i7-5820K Processor (15M Cache, up to 3.60 GHz) quick reference with specifications, features, and technologies.

Let’s not forget to Intel shipped the first multicore x86 processor.

Last edited:

- Joined

- Jun 14, 2020

- Messages

- 5,810 (3.13/day)

| System Name | Mean machine |

|---|---|

| Processor | AMD 6900HS |

| Memory | 2x16 GB 4800C40 |

| Video Card(s) | AMD Radeon 6700S |

6 cores have dropped in price, just not amds specifically. Intel offers mutli core cpus for cheaps.Oh really? That means with how much the 9600X costs a 6-core hasn't really dropped in price.

- Joined

- Jan 14, 2023

- Messages

- 939 (1.03/day)

| System Name | Lenovo slim 5 16' |

|---|---|

| Processor | AMD 8845hs |

| Motherboard | Lenovo motherboard |

| Cooling | 2 fans |

| Memory | 64gb 5600mhz cl40 |

| Video Card(s) | 4070 laptop |

| Storage | 16tb, x2 8tb SSD |

| Display(s) | 16in 16:10 (1920x1200) 144hz |

| Power Supply | 230w psu |

Those are designed differently, the AI HX chips are on a single monolithic die. 4 zen 5, and 8 zen 5c cores, plus the igpu on a single die.They probably the 2 CCX on Strix Point. Its wrong but I get how one would make that mistake.

- Joined

- Sep 1, 2020

- Messages

- 2,735 (1.54/day)

- Location

- Bulgaria

When? In same month in the same year with AMD 64 x2 and Intel CPU Pentium D in the name of the true was not multicore, just 2*1 cores glued together.Let’s not forget to Intel shipped the first multicore x86 processor.

Ps. AMD Thuban was first 6 core CPU for the consumers. The flagship from first series: Phenom II X6 1090T was with MSRP 295$.

- Joined

- Oct 3, 2024

- Messages

- 167 (0.58/day)

- Location

- Belgium

| System Name | The weirdo budget thingy |

|---|---|

| Processor | AMD Ryzen 7 9700X |

| Motherboard | ASRock B650M-HDV/M.2 |

| Cooling | Deepcool Gammaxx AG400 |

| Memory | Crucial 32GB DDR5-5600 CL46 (JEDEC) |

| Video Card(s) | AMD Radeon 610M |

| Storage | WD SN5000 1TB + 240GB Crucial BX500 + about 900GB worth of random SATA SSDs |

| Display(s) | Dell P2317H + repurposed Dell Latitude E6520 display (15" FHD IPS) |

| Case | Cooler Master MB600L v2 |

| Audio Device(s) | Sennheiser SP20 |

| Power Supply | Cooler Master MWE 550 Gold v3 |

| Mouse | Logitech M90 |

| Keyboard | Logitech K120 |

| VR HMD | N/A |

| Software | Fedora 42/Windows 10 Enterprise IoT LTSC |

| Benchmark Scores | coming soon! |

Yes, but the Zen 5 is on one CCX and the Zen 5c is on another. Don't confuse CCDs (compute chiplets), and CCX (core complexes of which mulitple can exist on a monolithic die).Those are designed differently, the AI HX chips are on a single monolithic die. 4 zen 5, and 8 zen 5c cores, plus the igpu on a single die.