- Joined

- May 21, 2024

- Messages

- 1,516 (3.59/day)

JEDEC Solid State Technology Association, the global leader in standards development for the microelectronics industry, today announced the publication of JESD209-6, the latest Low Power Double Data Rate 6 (LPDDR6) standard. JESD209-6 is designed to significantly boost memory speed and efficiency for a variety of uses including mobile devices and AI. The new JESD209-6 LPDDR6 standard represents a significant advancement in memory technology, offering enhanced performance, power efficiency, and security.

High Performance

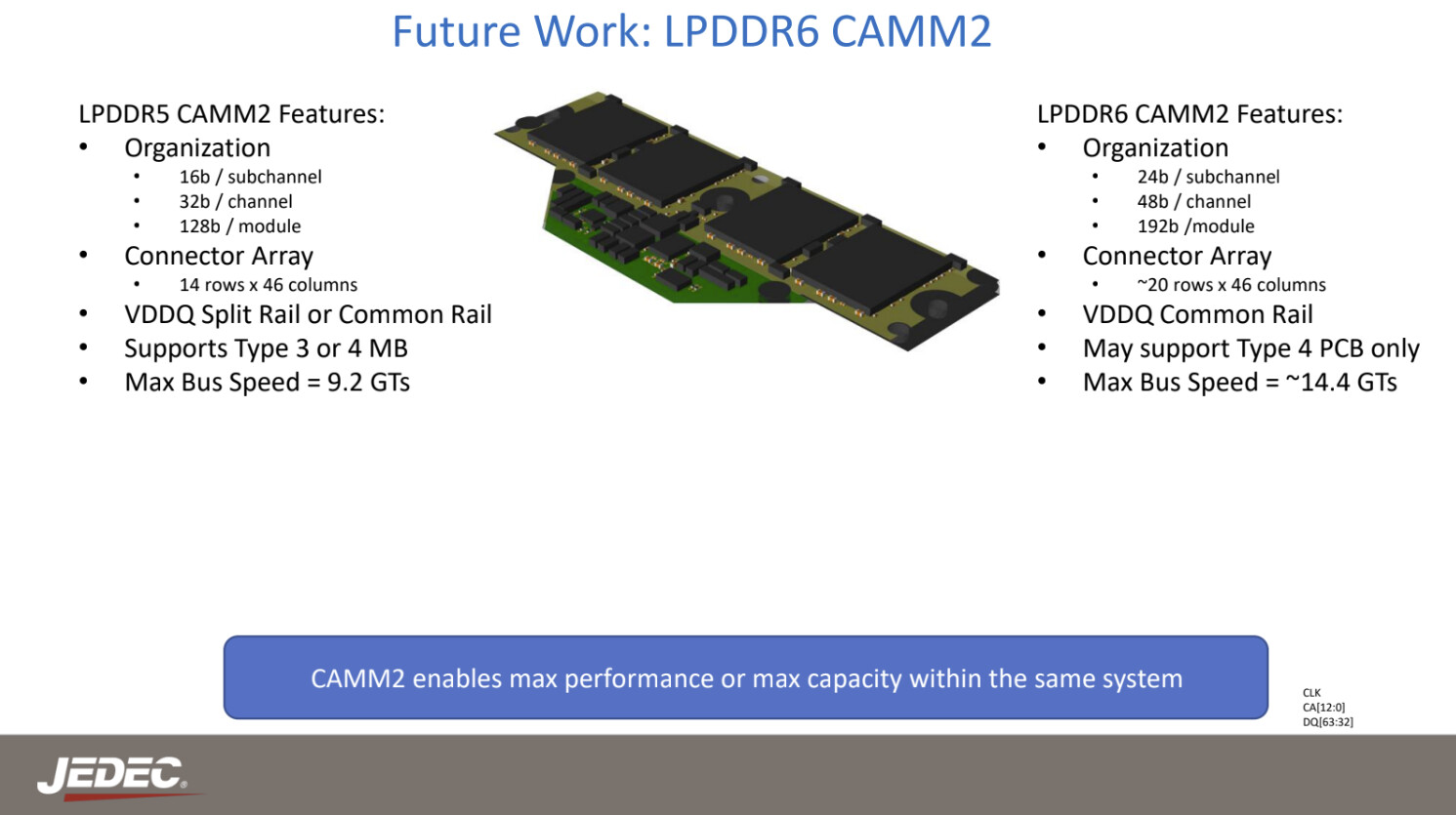

To enable AI applications and other high-performance workloads, LPDDR6 employs a dual sub-channel architecture that allows for flexible operation while maintaining a small access granularity of 32 bytes. In addition, LPDDR6 key features offer:

Power Efficiency

To help meet ever-increasing demands for power efficiency, LPDDR6 operates with a lower voltage and low power consumption capable VDD2 supply as compared to LPDDR5, and mandates two supplies for VDD2. Additional power-saving features include:

Security and Reliability

Security and reliability improvements over the previous version of the standard include:

Industry Support

"New generation low-power memory LPDDR6 offers significant performance improvements," said Vice-chair of the JC-42.6 Low Power Memory Subcommittee and chair of the LPDDR Task Group Osamu Nagashima of Advantest Corporation. "LPDDR6 will have a positive impact not only on mobile applications but on many other computing fields such as Edge AI computing, Client computer, data center and automotive."

"The requirements for AI inference continue to grow as AI models mature and are deployed throughout the network edge and in multiple endpoint devices. These edge devices demand high-performance processing and greater memory bandwidth while maintaining cost, power efficiency and reliability. LPDDR6 memory is an ideal solution, providing the speed, bandwidth and capacity needed to efficiently implement AI inference," said Boyd Phelps, Senior Vice President and General Manager of the Silicon Solutions Group at Cadence. "Cadence has cooperated closely with JEDEC during the LPDDR6 specification development, hosting many meetings on our campus. We offer our AI customers a variety of options for the highest-performance memory subsystems available."

Brig Asay, Senior Director, Network and Datacenter Solutions, Keysight Technologies, said: "Keysight is honored to be part of this new memory standard, which promises significant advancements in technology and efficiency. This new LPDDR6 standard is set to revolutionize the market by delivering unprecedented speed, and reliability, enabling the industry's AI Edge rollout. As the deployment and use of next-generation memory devices are growing, it will be a significant milestone in enabling faster time to market for LPDDR6 memory designs."

"MediaTek is prepared to support the new JEDEC LPDDR6 standard. This significant advancement in memory technology represents an ideal balance of power efficiency, robust security features, and enhanced performance, directly supporting our commitment to delivering high-performance, highly efficient SoC solutions across various products. We are confident that this new standard will spur innovations in mobile devices and AI applications, providing our products with the necessary memory capabilities to meet future demands."—Leo Shieh, General Manager of Silicon Product Development at MediaTek

"Memory performance is crucial to enabling a new era of smartphone and edge computing. At Micron, we are committed to accelerating innovation and are proud to have collaborated with industry leaders on LPDDR6 to define a standard that dramatically increases system performance while reducing power," said Mark Montierth, Corporate Vice President and General Manager of the Mobile and Client Business Unit at Micron Technology.

"Qualcomm Technologies, Inc. is a global leader in AI edge innovation and is proud to be one of the first in the industry to implement LPDDR6, addressing the demanding performance needs of advanced AI applications while significantly enhancing overall efficiency and reducing power consumption in system-on-a-chips (SoC). This achievement underscores our commitment to driving technological breakthroughs that redefine industry standards. The implementation of LPDDR6 is a key part of our mission to deliver best-in-class SoC solutions. By spearheading this initiative, we have united key industry players to support the seamless development and enablement of the LPDDR6 specification. Beyond the mobile industry, Qualcomm Technologies envisions LPDDR6 as an essential technology poised to revolutionize computing, automotive, AI, and other sectors, paving the way for transformative advancements in years to come," said Durga Malladi, SVP & GM, Technology Planning, Edge Solutions & Data Center, Qualcomm Technologies, Inc.

"Samsung believes that the establishment of the LPDDR6 JEDEC standard will play a pivotal role in accelerating the next generation of LPDDR products. We are honored to collaborate with the industry through JEDEC and sincerely appreciate the opportunity to contribute to this important milestone. As a technology leader, Samsung is committed to delivering JEDEC-compliant product to customers providing optimized solutions that address the evolving demands of the mobile market, including on-device AI," said Jangseok Choi, Vice President and Head of the Memory Product Planning Team at Samsung.

"SK hynix is proud to have contributed significantly to the development and standardization of LPDDR6 within JEDEC. LPDDR6 brings significant improvements in bandwidth and power efficiency, while also enhancing reliability features to meet the growing demands of next-generation mobile, automotive, and AI-driven applications. This standard reflects a step forward in delivering high-performance, low-power DRAM solutions with greater reliability across a wider range of use cases. We remain committed to advancing memory innovation in close collaboration with industry partners." Sangkwon Lee, Head of DRAM Product Planning and Enablement, SK hynix

"The adoption of AI in modern electronic systems is demanding rapid advancements in memory performance, power efficiency, and security," said Neeraj Paliwal, senior vice president, product management at Synopsys. "As an active contributing member of JEDEC for decades, Synopsys is driving the development and promotion of the new LPDDR6 standard. Adopted by multiple customers, companies are leveraging the industry-leading Synopsys LPDDR6 PHY, controller and verification IP solutions to integrate the standard into their high-density SoCs, ensuring the high bandwidth, reliability, and power efficiency required for mobile devices and AI systems."

View at TechPowerUp Main Site | Source

High Performance

To enable AI applications and other high-performance workloads, LPDDR6 employs a dual sub-channel architecture that allows for flexible operation while maintaining a small access granularity of 32 bytes. In addition, LPDDR6 key features offer:

- 2 sub-channels per die, 12 data signal lines (DQs) per sub-channel to optimize channel performance capabilities

- Each sub-channel includes 4 command/address (CA) signals, optimized to reduce ball count and improve data access speed

- Static efficiency mode designed to support high-capacity memory configurations and maximize bank resource utilization

- Flexible data access, on-the-fly burst length control to support 32B & 64B access

- Dynamic write NT-ODT (non-target on-die termination) enables the memory to adjust ODT based on workload demands, improving signal integrity

Power Efficiency

To help meet ever-increasing demands for power efficiency, LPDDR6 operates with a lower voltage and low power consumption capable VDD2 supply as compared to LPDDR5, and mandates two supplies for VDD2. Additional power-saving features include:

- Alternating clock command inputs are used to enhance performance and efficiency

- Dynamic Voltage Frequency Scaling for Low power (DVFSL) lowers the VDD2 supply during low-frequency operation to reduce power consumption

- Dynamic Efficiency mode utilizes a single sub-channel interface for low-power, low-bandwidth use cases

- Support for both partial self and active refresh to reduce refresh power usage

Security and Reliability

Security and reliability improvements over the previous version of the standard include:

- Per Row Activation Counting (PRAC) to support DRAM data integrity

- Carve-out Meta mode is defined to enhance overall system reliability by allocating specific memory regions for critical tasks

- Support for programmable link protection scheme and on-die error correction code (ECC)

- Capable of supporting Command/Address (CA) parity, error scrubbing, and memory built-in self-test (MBIST) for enhanced error detection and system reliability

"JEDEC is proud to introduce LPDDR6, the culmination of years of dedicated effort by members of the JC-42.6 Subcommittee for Low Power Memories," said Mian Quddus, JEDEC's Chairman of the Board of Directors. He added, "By delivering a balance of power efficiency, robust security options and high performance, LPDDR6 is an ideal choice for next-generation mobile devices, AI and related applications to thrive in a power-conscious, high-performance world."

Industry Support

"New generation low-power memory LPDDR6 offers significant performance improvements," said Vice-chair of the JC-42.6 Low Power Memory Subcommittee and chair of the LPDDR Task Group Osamu Nagashima of Advantest Corporation. "LPDDR6 will have a positive impact not only on mobile applications but on many other computing fields such as Edge AI computing, Client computer, data center and automotive."

"The requirements for AI inference continue to grow as AI models mature and are deployed throughout the network edge and in multiple endpoint devices. These edge devices demand high-performance processing and greater memory bandwidth while maintaining cost, power efficiency and reliability. LPDDR6 memory is an ideal solution, providing the speed, bandwidth and capacity needed to efficiently implement AI inference," said Boyd Phelps, Senior Vice President and General Manager of the Silicon Solutions Group at Cadence. "Cadence has cooperated closely with JEDEC during the LPDDR6 specification development, hosting many meetings on our campus. We offer our AI customers a variety of options for the highest-performance memory subsystems available."

Brig Asay, Senior Director, Network and Datacenter Solutions, Keysight Technologies, said: "Keysight is honored to be part of this new memory standard, which promises significant advancements in technology and efficiency. This new LPDDR6 standard is set to revolutionize the market by delivering unprecedented speed, and reliability, enabling the industry's AI Edge rollout. As the deployment and use of next-generation memory devices are growing, it will be a significant milestone in enabling faster time to market for LPDDR6 memory designs."

"MediaTek is prepared to support the new JEDEC LPDDR6 standard. This significant advancement in memory technology represents an ideal balance of power efficiency, robust security features, and enhanced performance, directly supporting our commitment to delivering high-performance, highly efficient SoC solutions across various products. We are confident that this new standard will spur innovations in mobile devices and AI applications, providing our products with the necessary memory capabilities to meet future demands."—Leo Shieh, General Manager of Silicon Product Development at MediaTek

"Memory performance is crucial to enabling a new era of smartphone and edge computing. At Micron, we are committed to accelerating innovation and are proud to have collaborated with industry leaders on LPDDR6 to define a standard that dramatically increases system performance while reducing power," said Mark Montierth, Corporate Vice President and General Manager of the Mobile and Client Business Unit at Micron Technology.

"Qualcomm Technologies, Inc. is a global leader in AI edge innovation and is proud to be one of the first in the industry to implement LPDDR6, addressing the demanding performance needs of advanced AI applications while significantly enhancing overall efficiency and reducing power consumption in system-on-a-chips (SoC). This achievement underscores our commitment to driving technological breakthroughs that redefine industry standards. The implementation of LPDDR6 is a key part of our mission to deliver best-in-class SoC solutions. By spearheading this initiative, we have united key industry players to support the seamless development and enablement of the LPDDR6 specification. Beyond the mobile industry, Qualcomm Technologies envisions LPDDR6 as an essential technology poised to revolutionize computing, automotive, AI, and other sectors, paving the way for transformative advancements in years to come," said Durga Malladi, SVP & GM, Technology Planning, Edge Solutions & Data Center, Qualcomm Technologies, Inc.

"Samsung believes that the establishment of the LPDDR6 JEDEC standard will play a pivotal role in accelerating the next generation of LPDDR products. We are honored to collaborate with the industry through JEDEC and sincerely appreciate the opportunity to contribute to this important milestone. As a technology leader, Samsung is committed to delivering JEDEC-compliant product to customers providing optimized solutions that address the evolving demands of the mobile market, including on-device AI," said Jangseok Choi, Vice President and Head of the Memory Product Planning Team at Samsung.

"SK hynix is proud to have contributed significantly to the development and standardization of LPDDR6 within JEDEC. LPDDR6 brings significant improvements in bandwidth and power efficiency, while also enhancing reliability features to meet the growing demands of next-generation mobile, automotive, and AI-driven applications. This standard reflects a step forward in delivering high-performance, low-power DRAM solutions with greater reliability across a wider range of use cases. We remain committed to advancing memory innovation in close collaboration with industry partners." Sangkwon Lee, Head of DRAM Product Planning and Enablement, SK hynix

"The adoption of AI in modern electronic systems is demanding rapid advancements in memory performance, power efficiency, and security," said Neeraj Paliwal, senior vice president, product management at Synopsys. "As an active contributing member of JEDEC for decades, Synopsys is driving the development and promotion of the new LPDDR6 standard. Adopted by multiple customers, companies are leveraging the industry-leading Synopsys LPDDR6 PHY, controller and verification IP solutions to integrate the standard into their high-density SoCs, ensuring the high bandwidth, reliability, and power efficiency required for mobile devices and AI systems."

View at TechPowerUp Main Site | Source