I noticed this really odd core usage behavior when running games. Processor is a Ryzen 3 3100 and I'm running the 1usmus Ryzen Universal power plan.

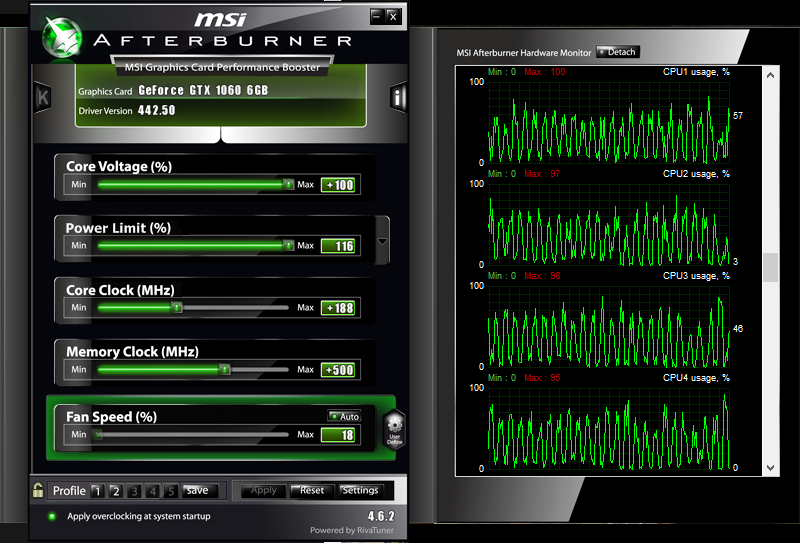

This one was while running a game with a 1000ms polling rate:

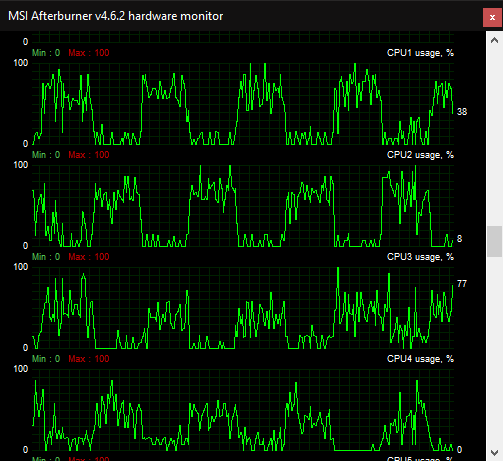

And this one was from running Cinebench R15 single core benchmark with a faster 100ms polling rate:

So as you can see, the processor keeps jumping between using the CPU1+CPU3 and CPU2+CPU4 cores.

There's no issues with actual performance at all, but this just seems like a very inefficient core utilization with a lot of unnecessary data transfer over the infinity fabric bus (which is already a limiting factor on the Ryzen 3100 2+2 core layout).

I did some Google searches and can't find forum posts where other people have noticed this same pattern.

Thought?

This one was while running a game with a 1000ms polling rate:

And this one was from running Cinebench R15 single core benchmark with a faster 100ms polling rate:

So as you can see, the processor keeps jumping between using the CPU1+CPU3 and CPU2+CPU4 cores.

There's no issues with actual performance at all, but this just seems like a very inefficient core utilization with a lot of unnecessary data transfer over the infinity fabric bus (which is already a limiting factor on the Ryzen 3100 2+2 core layout).

I did some Google searches and can't find forum posts where other people have noticed this same pattern.

Thought?