The performance of Bulldozer isn't relevant here.When "Bulldozer" was released how many PC CPUs (sold as new) had less FPU cores count compared to integer cores?

"Bulldozer" architecture was and still is a disgrace.

The FX-4100 running at 3,6Ghz (can boost to 3,8 Ghz) is advertised as a 4 cores cpu.

Athlon II x4 640 is running at 3 Ghz (no boost) and is a 4 cores cpu.

Main problem is that in single-threaded performance the FX-4100 is scaling worst that the Athlon II x4 640 and in term of multi-threaded performance the FX-4100 is actualy worst than the Athlon II x4 640.

So basicaly we had a newer architecture that had worst performance/clock compared to the older architecture. This is something that you see during development phase. So what's the point to push on the market a product that sucks compared to the older architecture?!?

Why AMD insisted with the Faildozer revisions is beyond my understanding. At that time the only real solution to upgrade from a K10 family cpu was an Intel CPU (visible in their shitty market share during Faildozer era).

If it was me taking the call at AMD after seeing how crap is the Faildozer architecture I would had see if it's possible to actually get a bit higher clocks from K10 family and add SSE 4.1/4.2 and AVX and actually try to work on a new CPU architecture (trust me without a single person that took part in the development of Faildozer).

Not really related to this topic. I kinda got tired and sick of people praising/defending AMD. They kinda forget that AMD actually wanted to sell Faildozer at some prices that have nothing to do with the reality of that architecture, that in Windows case AMD drivers were and still are pure junk, that AMD decided to no longer release drivers for Win 8.1 an use that still has more than 3 years to live, that each Ryzen release iteration has been full of problems (you kinda expect the 3rd iteration to be smooth but well not in AMD case... most likely because they just rush the products on the market without real testing something that I said about AMD 7 years ago). I'm not bashing AMD, just pointing to problems that AMD just doesn't care! I don't like Intel or Nvidia, the deal is that Intel, Nvidia and AMD have all 3 shady marketing technique (people accused NVIDIA of crippling the performance of older architectures in drivers, if you think AMD is better maybe you should check better because AMD might had done something that is far worst).

The value of Bulldozer isn't relevant here.

How "shady" various corporations is isn't relevant here, with the possible exception of pointing out that corporations are shady by definition because profit is extracted by selling things for more than their worth. In order to do that, people must be tricked into parting with more of their money than they should.

What is relevant is the technical definition of a core. As I already posted, FPUs are not even required to have a CPU core. Please, at least, try to rebut what I've said instead of ignoring my arguments entirely. I've done more than just point out that FPUs aren't required.

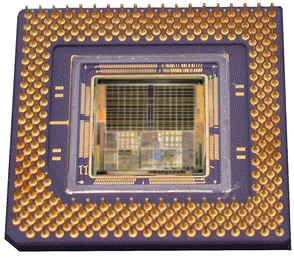

...and it's reflected in the increase of transistors too.

...and it's reflected in the increase of transistors too.