T0@st

News Editor

- Joined

- Mar 7, 2023

- Messages

- 3,328 (3.85/day)

- Location

- South East, UK

| System Name | The TPU Typewriter |

|---|---|

| Processor | AMD Ryzen 5 5600 (non-X) |

| Motherboard | GIGABYTE B550M DS3H Micro ATX |

| Cooling | DeepCool AS500 |

| Memory | Kingston Fury Renegade RGB 32 GB (2 x 16 GB) DDR4-3600 CL16 |

| Video Card(s) | PowerColor Radeon RX 7800 XT 16 GB Hellhound OC |

| Storage | Samsung 980 Pro 1 TB M.2-2280 PCIe 4.0 X4 NVME SSD |

| Display(s) | Lenovo Legion Y27q-20 27" QHD IPS monitor |

| Case | GameMax Spark M-ATX (re-badged Jonsbo D30) |

| Audio Device(s) | FiiO K7 Desktop DAC/Amp + Philips Fidelio X3 headphones, or ARTTI T10 Planar IEMs |

| Power Supply | ADATA XPG CORE Reactor 650 W 80+ Gold ATX |

| Mouse | Roccat Kone Pro Air |

| Keyboard | Cooler Master MasterKeys Pro L |

| Software | Windows 10 64-bit Home Edition |

HXL (@9550pro) has highlighted an intriguing pinned post on the Chinese Zhihu community site—where XZiar, a self described "Central Processing Unit (CPU) expert," has shared a very fuzzy/low quality screenshot of a Windows Task Manager session. The information on display indicates that a "Genuine Intel(R) 0000 1.0 GHz" processor was in use—perhaps a very early Lunar Lake (LNL) engineering sample (ES1). XZiar confirmed the pre-release nature of the onboard chip, and teased its performance prowess: "It's good to use the craftsmanship that others have stepped on. It can run 2.8 GHz with only A1 step, and it is very smooth."

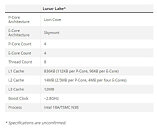

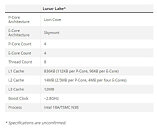

The "A1" designation implies that the leaked sample is among the first LNL processor prototypes to exit manufacturing facilities—Intel previewed its "Lunar Lake-MX" SoC package to press representatives last November. XZiar's followers have pored over the screenshot and ascertained that the leaked example sports a "8-core + 8-thread, without Hyperthreading, 4P+4LPE" configuration. Others were confused by the chip's somewhat odd on-board cache designations—L1: 836 KB, L2: 14 MB and L3: 12 MB—XZiar believes that prototype's setup "is obviously not up to par," when a replier compares the spec to an N300 series processor. It is theorized that Windows Task Manager is simply not fully capable of detecting the sample's full makeup, but XZiar reckons that 12 MB of L3 cache is the correct figure.

A Tom's Hardware article has similarly analyzed the A1 chip's screenshot credentials—they have compiled this data into a speculative specification sheet (see above). They noted a couple of differences—when compared to Intel's current mobile CPU generation: "The L1 cache designation implies that Lunar Lake doesn't come with any low-power E-Cores like Meteor Lake, or all are low-power but with increased L1 cache size. The 2.8 GHz boost clock is also unsurprising since the sample is likely ES silicon...Things get weird when you start looking at the cache, though. It would appear Lunar Lake is identical to Meteor Lake in the L1 and L2 cache, or at least that's what the screenshot implies. However, the Lunar Lake sample has only 12 MB of L3 cache, lower than the 14 MB of L2 cache. Usually, a higher level of cache means more capacity, and often significantly more, so it's very unintuitive that Lunar Lake should have less L3 than L2 cache. This directly contradicts an earlier leak that showed 16 MB of L3 cache for Lunar Lake but has identical specifications otherwise."

They also took issue with the sample's alleged thread count (just eight): "Intel's previous hybrid architecture CPUs have included Hyper-Threading for the P-Cores, which should result in 12 threads. Since A1 silicon is unlikely to be the final product, it's possible it's simply disabled because of technical issues or for testing purposes. On the other hand, early Arrow Lake samples don't have Hyper-Threading either. Although that could be a coincidence, it raises the possibility that Intel may be moving on from Hyper-Threading in 2024."

View at TechPowerUp Main Site | Source

The "A1" designation implies that the leaked sample is among the first LNL processor prototypes to exit manufacturing facilities—Intel previewed its "Lunar Lake-MX" SoC package to press representatives last November. XZiar's followers have pored over the screenshot and ascertained that the leaked example sports a "8-core + 8-thread, without Hyperthreading, 4P+4LPE" configuration. Others were confused by the chip's somewhat odd on-board cache designations—L1: 836 KB, L2: 14 MB and L3: 12 MB—XZiar believes that prototype's setup "is obviously not up to par," when a replier compares the spec to an N300 series processor. It is theorized that Windows Task Manager is simply not fully capable of detecting the sample's full makeup, but XZiar reckons that 12 MB of L3 cache is the correct figure.

A Tom's Hardware article has similarly analyzed the A1 chip's screenshot credentials—they have compiled this data into a speculative specification sheet (see above). They noted a couple of differences—when compared to Intel's current mobile CPU generation: "The L1 cache designation implies that Lunar Lake doesn't come with any low-power E-Cores like Meteor Lake, or all are low-power but with increased L1 cache size. The 2.8 GHz boost clock is also unsurprising since the sample is likely ES silicon...Things get weird when you start looking at the cache, though. It would appear Lunar Lake is identical to Meteor Lake in the L1 and L2 cache, or at least that's what the screenshot implies. However, the Lunar Lake sample has only 12 MB of L3 cache, lower than the 14 MB of L2 cache. Usually, a higher level of cache means more capacity, and often significantly more, so it's very unintuitive that Lunar Lake should have less L3 than L2 cache. This directly contradicts an earlier leak that showed 16 MB of L3 cache for Lunar Lake but has identical specifications otherwise."

They also took issue with the sample's alleged thread count (just eight): "Intel's previous hybrid architecture CPUs have included Hyper-Threading for the P-Cores, which should result in 12 threads. Since A1 silicon is unlikely to be the final product, it's possible it's simply disabled because of technical issues or for testing purposes. On the other hand, early Arrow Lake samples don't have Hyper-Threading either. Although that could be a coincidence, it raises the possibility that Intel may be moving on from Hyper-Threading in 2024."

View at TechPowerUp Main Site | Source