- Joined

- Oct 9, 2007

- Messages

- 47,670 (7.43/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

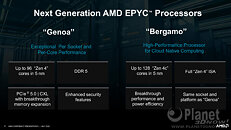

AMD is launching two distinct classes of next-generation enterprise processors, the 4th Generation EPYC "Genoa" with CPU core-counts up to 96-core/192-thread; and the new EPYC "Bergamo" with a massive 128-core/256-thread compute density. Pictures of the "Genoa" MCM are already out in the wild, revealing twelve "Zen 4" CCDs built on 5 nm, and a new-generation sIOD (I/O die) that's very likely built on 6 nm. The fiberglass substrate of "Genoa" already looks crowded with twelve chiplets, making us wonder if AMD needed a larger package for "Bergamo." Turns out, it doesn't.

In its latest Corporate presentation, AMD reiterated that "Bergamo" will be based on the same SP5 (LGA-6096) package as "Genoa." This would mean that the company either made room for more CCDs, or the CCDs themselves are larger in size. AMD states that "Bergamo" CCDs are based on the "Zen 4c" microarchitecture. Details about "Zen 4c" are scarce, but from what we gather, it is a cloud-optimized variant of "Zen 4" probably with the entire ISA of "Zen 4," and power characteristics suited for high-density cloud environments. These chiplets are built on the same TSMC N5 (5 nm EUV) process as the regular "Zen 4" CCDs.

View at TechPowerUp Main Site | Source

In its latest Corporate presentation, AMD reiterated that "Bergamo" will be based on the same SP5 (LGA-6096) package as "Genoa." This would mean that the company either made room for more CCDs, or the CCDs themselves are larger in size. AMD states that "Bergamo" CCDs are based on the "Zen 4c" microarchitecture. Details about "Zen 4c" are scarce, but from what we gather, it is a cloud-optimized variant of "Zen 4" probably with the entire ISA of "Zen 4," and power characteristics suited for high-density cloud environments. These chiplets are built on the same TSMC N5 (5 nm EUV) process as the regular "Zen 4" CCDs.

View at TechPowerUp Main Site | Source