- Joined

- Oct 9, 2007

- Messages

- 47,733 (7.42/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

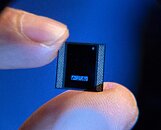

The fingernail-size Intel chip with Foveros technology is a first-of-its kind. With Foveros, processors are built in a totally new way: not with the various IPs spread out flat in two dimensions, but with them stacked in three dimensions. Think of a chip designed as a layer cake (a 1-millimeter-thick layer cake) versus a chip with a more-traditional pancake-like design. Intel's Foveros advanced packaging technology allows Intel to "mix and match" technology IP blocks with various memory and I/O elements - all in a small physical package for significantly reduced board size. The first product designed this way is "Lakefield," the Intel Core processor with Intel hybrid technology.

Industry analyst firm The Linley Group recently named Intel's Foveros 3D-stacking technology as "Best Technology" in its 2019 Analysts' Choice Awards. "Our awards program not only recognizes excellence in chip design and innovation, but also acknowledges the products that our analysts believe will have an impact on future designs," said Linley Gwennap, of The Linley Group.

For its part, Lakefield represents an entirely new class of chip. It delivers an optimal balance of performance and efficiency with best-in-class connectivity in a small footprint - Lakefield's package area measures just 12-by-12-by-1 millimeters. Its hybrid CPU architecture combines power-efficient "Tremont" cores with a performance scalable 10 nm "Sunny Cove" core to intelligently deliver productivity performance when needed and power-sipping efficiency when not needed for long battery life.

These benefits offer original equipment manufacturers more flexibility for thin-and-light form factor PCs, including the emerging dual-screen and foldable screen PC categories.

Recently, three designs have been announced that are powered by Lakefield and were co-engineered with Intel. In October 2019, Microsoft previewed the Surface Neo, a dual-screen device. And later that month at its developer conference, Samsung announced the Galaxy Book S. Unveiled at CES 2020 and expected to ship midyear is the Lenovo ThinkPad X1 Fold.

View at TechPowerUp Main Site

Industry analyst firm The Linley Group recently named Intel's Foveros 3D-stacking technology as "Best Technology" in its 2019 Analysts' Choice Awards. "Our awards program not only recognizes excellence in chip design and innovation, but also acknowledges the products that our analysts believe will have an impact on future designs," said Linley Gwennap, of The Linley Group.

For its part, Lakefield represents an entirely new class of chip. It delivers an optimal balance of performance and efficiency with best-in-class connectivity in a small footprint - Lakefield's package area measures just 12-by-12-by-1 millimeters. Its hybrid CPU architecture combines power-efficient "Tremont" cores with a performance scalable 10 nm "Sunny Cove" core to intelligently deliver productivity performance when needed and power-sipping efficiency when not needed for long battery life.

These benefits offer original equipment manufacturers more flexibility for thin-and-light form factor PCs, including the emerging dual-screen and foldable screen PC categories.

Recently, three designs have been announced that are powered by Lakefield and were co-engineered with Intel. In October 2019, Microsoft previewed the Surface Neo, a dual-screen device. And later that month at its developer conference, Samsung announced the Galaxy Book S. Unveiled at CES 2020 and expected to ship midyear is the Lenovo ThinkPad X1 Fold.

View at TechPowerUp Main Site