They will in all likelihood disable the extra threads on consumer chips, as many rumors have been predicting/speculating over the last few months.This will be terrible for gaming. Server operators will rejoice at this news but...this is very likely to be harmful in the consumer space.

-

Welcome to TechPowerUp Forums, Guest! Please check out our forum guidelines for info related to our community.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD Could Release Next Generation EPYC CPUs with Four-Way SMT

- Thread starter AleksandarK

- Start date

FordGT90Concept

"I go fast!1!11!1!"

- Joined

- Oct 13, 2008

- Messages

- 26,263 (4.30/day)

- Location

- IA, USA

| System Name | BY-2021 |

|---|---|

| Processor | AMD Ryzen 7 5800X (65w eco profile) |

| Motherboard | MSI B550 Gaming Plus |

| Cooling | Scythe Mugen (rev 5) |

| Memory | 2 x Kingston HyperX DDR4-3200 32 GiB |

| Video Card(s) | AMD Radeon RX 7900 XT |

| Storage | Samsung 980 Pro, Seagate Exos X20 TB 7200 RPM |

| Display(s) | Nixeus NX-EDG274K (3840x2160@144 DP) + Samsung SyncMaster 906BW (1440x900@60 HDMI-DVI) |

| Case | Coolermaster HAF 932 w/ USB 3.0 5.25" bay + USB 3.2 (A+C) 3.5" bay |

| Audio Device(s) | Realtek ALC1150, Micca OriGen+ |

| Power Supply | Enermax Platimax 850w |

| Mouse | Nixeus REVEL-X |

| Keyboard | Tesoro Excalibur |

| Software | Windows 10 Home 64-bit |

| Benchmark Scores | Faster than the tortoise; slower than the hare. |

Sony and Microsoft will not be interested in 4-way SMT in future consoles, for example. That's tens of millions of units, potentially into the hundreds of millions.There seems to be this shortcut to thinking that so many "gamers" [that claim to be enthusiasts] constantly perform, namely the completely unfounded assumption and belief that "gaming" comprises the majority of use cases for x86 CPUs and that "gaming", and pleasing gamers, is the paramount concern, or should be, of AMD/Intel when that's not the case.

For all the people that know so little about processors:

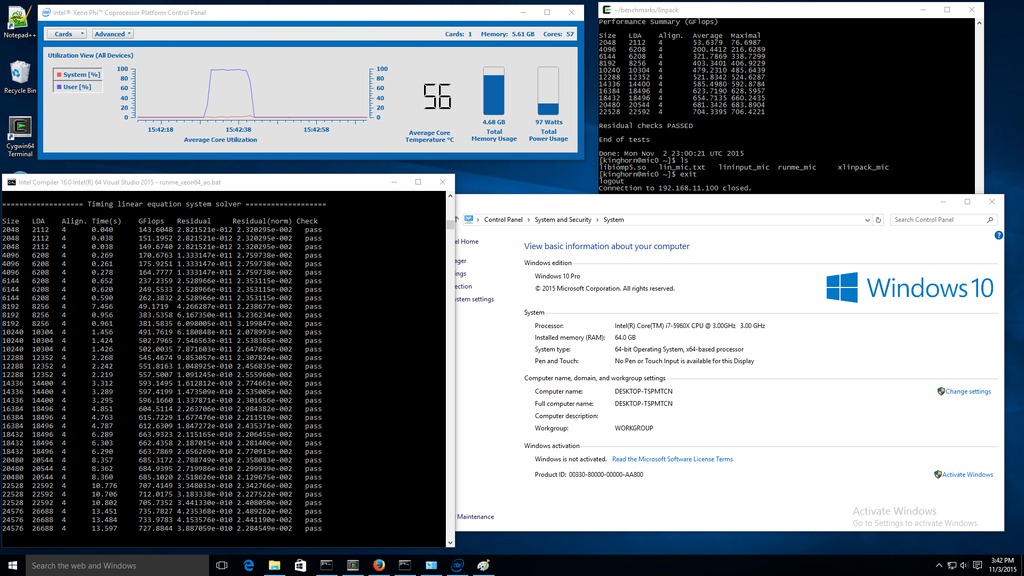

1) Intel offered 4 threads per core in Xeon Phi.

2) 4-way SMT was also included in processors by IBM, Sun and MIPS.

So despite AMD being called "innovative" by some in this thread, they're actually pretty late with this feature.

Sorry to ruin the AMD hype party.

Moreover, there's not much gain from 4-way SMT in general tasks, so don't expect this to be magically twice as fast. This works best in highly optimized compute clusters.

1) Intel offered 4 threads per core in Xeon Phi.

2) 4-way SMT was also included in processors by IBM, Sun and MIPS.

So despite AMD being called "innovative" by some in this thread, they're actually pretty late with this feature.

Sorry to ruin the AMD hype party.

Moreover, there's not much gain from 4-way SMT in general tasks, so don't expect this to be magically twice as fast. This works best in highly optimized compute clusters.

- Joined

- Mar 10, 2010

- Messages

- 11,880 (2.12/day)

- Location

- Manchester uk

| System Name | RyzenGtEvo/ Asus strix scar II |

|---|---|

| Processor | Amd R5 5900X/ Intel 8750H |

| Motherboard | Crosshair hero8 impact/Asus |

| Cooling | 360EK extreme rad+ 360$EK slim all push, cpu ek suprim Gpu full cover all EK |

| Memory | Gskill Trident Z 3900cas18 32Gb in four sticks./16Gb/16GB |

| Video Card(s) | Asus tuf RX7900XT /Rtx 2060 |

| Storage | Silicon power 2TB nvme/8Tb external/1Tb samsung Evo nvme 2Tb sata ssd/1Tb nvme |

| Display(s) | Samsung UAE28"850R 4k freesync.dell shiter |

| Case | Lianli 011 dynamic/strix scar2 |

| Audio Device(s) | Xfi creative 7.1 on board ,Yamaha dts av setup, corsair void pro headset |

| Power Supply | corsair 1200Hxi/Asus stock |

| Mouse | Roccat Kova/ Logitech G wireless |

| Keyboard | Roccat Aimo 120 |

| VR HMD | Oculus rift |

| Software | Win 10 Pro |

| Benchmark Scores | laptop Timespy 6506 |

True but they do buy custom chips based on Ip , they don't necessarily use all of it plus the cache and resources would likely increase for smt4 which would marginally improve smt2 performance if they cut smt 4 functions.Sony and Microsoft will not be interested in 4-way SMT in future consoles, for example. That's tens of millions of units, potentially into the hundreds of millions.

- Joined

- Nov 4, 2005

- Messages

- 12,194 (1.70/day)

| System Name | Compy 386 |

|---|---|

| Processor | 7800X3D |

| Motherboard | Asus |

| Cooling | Air for now..... |

| Memory | 64 GB DDR5 6400Mhz |

| Video Card(s) | 7900XTX 310 Merc |

| Storage | Samsung 990 2TB, 2 SP 2TB SSDs, 24TB Enterprise drives |

| Display(s) | 55" Samsung 4K HDR |

| Audio Device(s) | ATI HDMI |

| Mouse | Logitech MX518 |

| Keyboard | Razer |

| Software | A lot. |

| Benchmark Scores | Its fast. Enough. |

Windows 10 with Xeon Phi

Can you use an Intel Xeon Phi with Windows 10? Yes, you can. However, just because you can do something, doesn't mean that you should do it! I did a set up and a little testing mainly just to see if it would work -- it does!www.pugetsystems.com

If you can run an O.S. on it, it's a general purpose microprocessor, and I think that qualifies it for this discussion.

LOL, people have created "processors" in minecraft. Windows 10 has RISC versions for awhile.

Now Microsoft ports Windows 10, Linux to homegrown CPU design

MSR's E2 processor EDGEs into public view... with a little help from Qualcomm, too

Does it mean its a good idea? No. So how about semantics of three layer deep "we could, but should we?" is left alone and we focus on what going to improve performance.

Yeah well sorry to burst your bubble but Phi was a huge failure in the end, so bad that Intel couldn't pay others to take the remaining chips off of them.So despite AMD being called "innovative" by some in this thread, they're actually pretty late with this feature.

Sorry to ruin the AMD hype party.

- Joined

- Sep 24, 2019

- Messages

- 64 (0.03/day)

LOL, people have created "processors" in minecraft. Windows 10 has RISC versions for awhile.

Now Microsoft ports Windows 10, Linux to homegrown CPU design

MSR's E2 processor EDGEs into public view... with a little help from Qualcomm, toowww.theregister.co.uk

Does it mean its a good idea? No. So how about semantics of three layer deep "we could, but should we?" is left alone and we focus on what going to improve performance.

The proposition was raised that Intel had not yet created a processor with 4-way SMT. They have. /end discussion

People here said this is something Intel can't do. It's not true. End of story.Yeah well sorry to burst your bubble but Phi was a huge failure in the end, so bad that Intel couldn't pay others to take the remaining chips off of them.

And Phi wasn't a failure because of its SMT implementation.

- Joined

- Nov 4, 2005

- Messages

- 12,194 (1.70/day)

| System Name | Compy 386 |

|---|---|

| Processor | 7800X3D |

| Motherboard | Asus |

| Cooling | Air for now..... |

| Memory | 64 GB DDR5 6400Mhz |

| Video Card(s) | 7900XTX 310 Merc |

| Storage | Samsung 990 2TB, 2 SP 2TB SSDs, 24TB Enterprise drives |

| Display(s) | 55" Samsung 4K HDR |

| Audio Device(s) | ATI HDMI |

| Mouse | Logitech MX518 |

| Keyboard | Razer |

| Software | A lot. |

| Benchmark Scores | Its fast. Enough. |

The proposition was raised that Intel had not yet created a processor with 4-way SMT. They have. /end discussion

HAHAHAHA, /end discussion

Nah brah. I never said Intel didn't have it, if I did, good job on proving they had it on a niche product that doesn't matter, I was discussing how it might affect the performance of the core. Intel has it, but it sucked, IBM has it, and it works. AMD is going to try it, and its probably better left in server space.

You replied to my comment about the difference in CISC and RISC designs with a statement that Phi ran Windows 10, poorly, I can make things that work good work poorly as well, but in the name of time and sanity I choose not to. But /end discussion..... thats awesome. Go you.... far away.

- Joined

- Dec 29, 2010

- Messages

- 3,905 (0.74/day)

| Processor | AMD 5900x |

|---|---|

| Motherboard | Asus x570 Strix-E |

| Cooling | Hardware Labs |

| Memory | G.Skill 4000c17 2x16gb |

| Video Card(s) | RTX 3090 |

| Storage | Sabrent |

| Display(s) | Samsung G9 |

| Case | Phanteks 719 |

| Audio Device(s) | Fiio K5 Pro |

| Power Supply | EVGA 1000 P2 |

| Mouse | Logitech G600 |

| Keyboard | Corsair K95 |

I highly doubt AMD is going to divorce the core design between Epyc and Ryzen. If they are, it's fine; if not, AMD is pulling another Bulldozer with this one.

Yea, totally because AMD don't know what they are doing am I right?

- Joined

- Sep 24, 2019

- Messages

- 64 (0.03/day)

It wasn't a processor, it was a co-processor specifically designed for HPC

And you can run an Operating System on it. It's based on Pentium micro-architecture, and it runs general purpose x86 code natively.

How much more does this duck need to quack?

- Joined

- Sep 24, 2019

- Messages

- 64 (0.03/day)

HAHAHAHA, /end discussion

Nah brah. I never said Intel didn't have it, if I did, good job on proving they had it on a niche product that doesn't matter, I was discussing how it might affect the performance of the core. Intel has it, but it sucked, IBM has it, and it works. AMD is going to try it, and its probably better left in server space.

You replied to my comment about the difference in CISC and RISC designs with a statement that Phi ran Windows 10, poorly, I can make things that work good work poorly as well, but in the name of time and sanity I choose not to. But /end discussion..... thats awesome. Go you.... far away.

Sorry for quoting your entire post.

Given the fact that I did not mention CISC or RISC in my response, it's pretty obvious I wasn't commenting on that portion of your post.

A co-processor is still a processor. It's just put in a different place in a server, so it gets a fancy name.It wasn't a processor, it was a co-processor specifically designed for HPC

Phi is x86 compliant. People have successfully run OSes on it (even Windows).

Xeon Scalable is an evolution of Phi, so it shouldn't be hard for Intel to include 4-way SMT.

- Joined

- Sep 24, 2019

- Messages

- 64 (0.03/day)

I'm not sure, does running windows on x86 now counts as a special achievement?

How much more context do we need to clarify this matter? Are we reading different threads or something?

Aldain said this:

Are you F stupid?? When did intel implement 4 way smt??

I responded with information about Intel microprocessors which feature 4-way SMT.

Any commentary on the economic or technical success of products derived from this micro-architecture have no bearing on the fact that it exists.

D

Deleted member 185158

Guest

Lol. 320w cpu @ 1.1-1.3ghz .... designed for cloud computing. (had to research it)

Umm, I'll take the AMD SMT (any) desktop processor at 105w @ 3.8ghz instead lol.

Umm, I'll take the AMD SMT (any) desktop processor at 105w @ 3.8ghz instead lol.

- Joined

- Nov 4, 2005

- Messages

- 12,194 (1.70/day)

| System Name | Compy 386 |

|---|---|

| Processor | 7800X3D |

| Motherboard | Asus |

| Cooling | Air for now..... |

| Memory | 64 GB DDR5 6400Mhz |

| Video Card(s) | 7900XTX 310 Merc |

| Storage | Samsung 990 2TB, 2 SP 2TB SSDs, 24TB Enterprise drives |

| Display(s) | 55" Samsung 4K HDR |

| Audio Device(s) | ATI HDMI |

| Mouse | Logitech MX518 |

| Keyboard | Razer |

| Software | A lot. |

| Benchmark Scores | Its fast. Enough. |

And you can run an Operating System on it. It's based on Pentium micro-architecture, and it runs general purpose x86 code natively.

How much more does this duck need to quack?

I need it to quack 4 quacks simultaneously per core while running Crysis at 4K. Can it do that? Can I surf the web while using a USB to serial adapter to download software to a device, while listening to music, while using a USB to CAN protocol adapter to configure or load firmware to other nodes and fit in my laptop bag?

- Joined

- Mar 10, 2010

- Messages

- 11,880 (2.12/day)

- Location

- Manchester uk

| System Name | RyzenGtEvo/ Asus strix scar II |

|---|---|

| Processor | Amd R5 5900X/ Intel 8750H |

| Motherboard | Crosshair hero8 impact/Asus |

| Cooling | 360EK extreme rad+ 360$EK slim all push, cpu ek suprim Gpu full cover all EK |

| Memory | Gskill Trident Z 3900cas18 32Gb in four sticks./16Gb/16GB |

| Video Card(s) | Asus tuf RX7900XT /Rtx 2060 |

| Storage | Silicon power 2TB nvme/8Tb external/1Tb samsung Evo nvme 2Tb sata ssd/1Tb nvme |

| Display(s) | Samsung UAE28"850R 4k freesync.dell shiter |

| Case | Lianli 011 dynamic/strix scar2 |

| Audio Device(s) | Xfi creative 7.1 on board ,Yamaha dts av setup, corsair void pro headset |

| Power Supply | corsair 1200Hxi/Asus stock |

| Mouse | Roccat Kova/ Logitech G wireless |

| Keyboard | Roccat Aimo 120 |

| VR HMD | Oculus rift |

| Software | Win 10 Pro |

| Benchmark Scores | laptop Timespy 6506 |

That's nonesense, the server blades to run cloud xbox and ps5 games, are going to be made using epyc a special one too?epyc is not for gaming.

will likely never be introduced to gaming pc.

there's a way to fit 4 8 core cxx's onto a die.why go with 4 way smt ? that's only beneficial when you're maxing out cores on the die.

edited for clarity

edited for clarity

Last edited:

Yes & what was your point exactly, that 4 way SMT for AMD is not a major achievement ~ sure, I guess this why highlighting a product which was supposed to compete in HPC, but failed spectacularly is something noteworthy then?A co-processor is still a processor. It's just put in a different place in a server, so it gets a fancy name.

Phi is x86 compliant. People have successfully run OSes on it (even Windows).

Your point is noted, now remind us why running an OS on it is probably listed as an achievement(?) when it failed at its primary task?How much more context do we need to clarify this matter? Are we reading different threads or something?

- Joined

- Sep 24, 2019

- Messages

- 64 (0.03/day)

I need it to quack 4 quacks simultaneously per core while running Crysis at 4K. Can it do that? Can I surf the web while using a USB to serial adapter to download software to a device, while listening to music, while using a USB to CAN protocol adapter to configure or load firmware to other nodes and fit in my laptop bag?

If it can't run Crysis is it not a CPU in your opinion?

Guess the 90% of CPUs throughout history that don't utilize the x86 ISA aren't CPUs in your book.

Must be hard being that myopic. What's your prescription?

Yes & what was your point exactly, that 4 way SMT for AMD is not a major achievement ~ sure, I guess this why highlighting a product which was supposed to compete in HPC, but failed spectacularly is something noteworthy then?

This isn't anywhere near as difficult as you're making this. Aldain said "Intel never made a CPU with 4-way SMT", I provided the proof that they have. I made no commentary on its success or viability as a commercial product.

- Joined

- Aug 6, 2017

- Messages

- 7,412 (2.56/day)

- Location

- Poland

| System Name | Purple rain |

|---|---|

| Processor | 10.5 thousand 4.2G 1.1v |

| Motherboard | Zee 490 Aorus Elite |

| Cooling | Noctua D15S |

| Memory | 16GB 4133 CL16-16-16-31 Viper Steel |

| Video Card(s) | RTX 2070 Super Gaming X Trio |

| Storage | SU900 128,8200Pro 1TB,850 Pro 512+256+256,860 Evo 500,XPG950 480, Skyhawk 2TB |

| Display(s) | Acer XB241YU+Dell S2716DG |

| Case | P600S Silent w. Alpenfohn wing boost 3 ARGBT+ fans |

| Audio Device(s) | K612 Pro w. FiiO E10k DAC,W830BT wireless |

| Power Supply | Superflower Leadex Gold 850W |

| Mouse | G903 lightspeed+powerplay,G403 wireless + Steelseries DeX + Roccat rest |

| Keyboard | HyperX Alloy SilverSpeed (w.HyperX wrist rest),Razer Deathstalker |

| Software | Windows 10 |

| Benchmark Scores | A LOT |

please say that again in English.That's nonesense, the blades to run cloud xbox and ps5 games are going to be made using epyc a special one too?

- Joined

- Mar 10, 2010

- Messages

- 11,880 (2.12/day)

- Location

- Manchester uk

| System Name | RyzenGtEvo/ Asus strix scar II |

|---|---|

| Processor | Amd R5 5900X/ Intel 8750H |

| Motherboard | Crosshair hero8 impact/Asus |

| Cooling | 360EK extreme rad+ 360$EK slim all push, cpu ek suprim Gpu full cover all EK |

| Memory | Gskill Trident Z 3900cas18 32Gb in four sticks./16Gb/16GB |

| Video Card(s) | Asus tuf RX7900XT /Rtx 2060 |

| Storage | Silicon power 2TB nvme/8Tb external/1Tb samsung Evo nvme 2Tb sata ssd/1Tb nvme |

| Display(s) | Samsung UAE28"850R 4k freesync.dell shiter |

| Case | Lianli 011 dynamic/strix scar2 |

| Audio Device(s) | Xfi creative 7.1 on board ,Yamaha dts av setup, corsair void pro headset |

| Power Supply | corsair 1200Hxi/Asus stock |

| Mouse | Roccat Kova/ Logitech G wireless |

| Keyboard | Roccat Aimo 120 |

| VR HMD | Oculus rift |

| Software | Win 10 Pro |

| Benchmark Scores | laptop Timespy 6506 |

this is the post that started the Amd are copying intel with smt sentiment, already proven as baseless, regardless intel have not YET made smt4 earn them good repeatable money yet.So, they are now just doing what INTEL has been doing all along, except for the die shrinkage issue. More density is what INTEL has had Over AMD up until now.

NOTHING Innovative about that, at all. AND Amd is about to even start using the +++ HA HA!

AMD, just like apple, nothing new, just copy other peoples ideas and claim as if they thought of it themselves.

- Joined

- Dec 29, 2010

- Messages

- 3,905 (0.74/day)

| Processor | AMD 5900x |

|---|---|

| Motherboard | Asus x570 Strix-E |

| Cooling | Hardware Labs |

| Memory | G.Skill 4000c17 2x16gb |

| Video Card(s) | RTX 3090 |

| Storage | Sabrent |

| Display(s) | Samsung G9 |

| Case | Phanteks 719 |

| Audio Device(s) | Fiio K5 Pro |

| Power Supply | EVGA 1000 P2 |

| Mouse | Logitech G600 |

| Keyboard | Corsair K95 |

Any commentary on the economic or technical success of products derived from this micro-architecture have no bearing on the fact that it exists.

Neener neener?

Turds are turds, even if yer first with a turd?

D

Deleted member 185158

Guest

this is the post that started the Amd are copying intel with smt sentiment, already proven as baseless, regardless intel have not YET made smt4 earn them good repeatable money yet.

AMD SMT and Intel HT are not the same, they are and aren't. It's like a redhead vs a blonde.