-

Welcome to TechPowerUp Forums, Guest! Please check out our forum guidelines for info related to our community.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

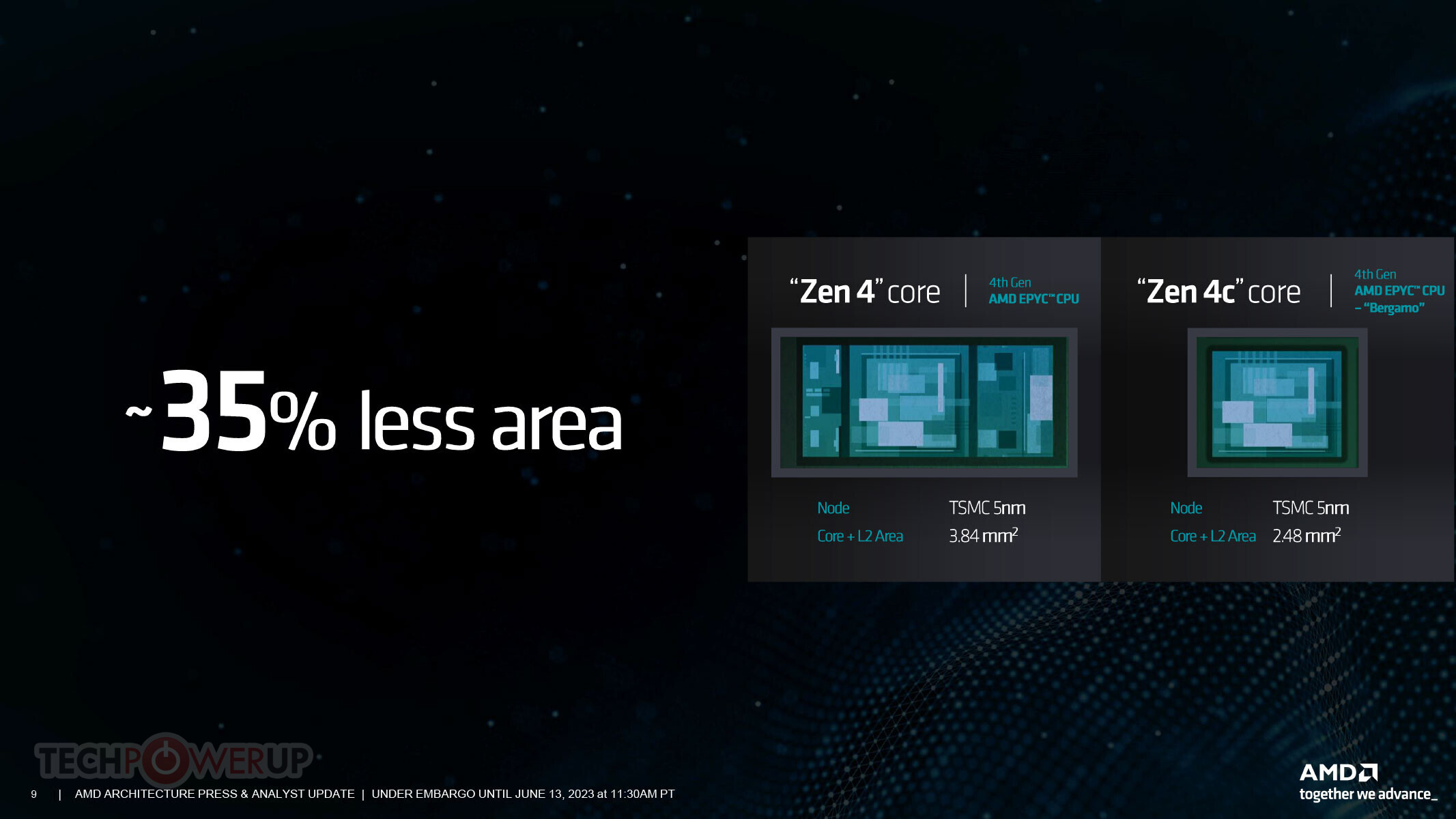

AMD Zen 4c Not an E-core, 35% Smaller than Zen 4, but with Identical IPC

- Thread starter btarunr

- Start date

- Joined

- Feb 1, 2019

- Messages

- 4,053 (1.72/day)

- Location

- UK, Midlands

| System Name | Main PC |

|---|---|

| Processor | 13700k |

| Motherboard | Asrock Z690 Steel Legend D4 - Bios 13.02 |

| Cooling | Noctua NH-D15S |

| Memory | 32 Gig 3200CL14 |

| Video Card(s) | 4080 RTX SUPER FE 16G |

| Storage | 1TB 980 PRO, 2TB SN850X, 2TB DC P4600, 1TB 860 EVO, 4TB WD SA510, 2x 3TB WD Red, 1x 4TB WD Red |

| Display(s) | LG 27GL850 |

| Case | Fractal Define R4 |

| Audio Device(s) | Soundblaster AE-9 |

| Power Supply | Antec HCG 750 Gold |

| Software | Windows 10 21H2 LTSC |

With my experimenting, (albeit on windows 10 which doesnt have intels pre configured scheduler).It's all good, I just loathe intels E-cores because they used a name that is the exact opposite of the product to mislead people about them

They're more efficient at single threaded tasks, and then intel uses them exclusively for multi threaded tasks.

Just... Ugh.

By default in Windows 10 e-cores are heavily favoured, pretty much all single threaded tasks are loaded on to them and p-cores are parked, this even happens if parking is disabled in the power profile. (ultimate performance). park control also cant override this behaviour.

If I adjust the hetergeneous thread scheduling policy, I can manipulate this behaviour, its a hidden setting in windows. Setting it to either "all processors" or "performant" starts letting p-cores to be used, the latter however almost blocks use of e-cores so not ideal if you still want them to be used. But would be a quick and dirty fix e.g. if you want to fire up a single threaded game, it would give you a almost certainty it would use a p-core and not have to worry about affinity settings. Could use with something like 'AutoPowerOptionsOk' to automate the solution. Setting it to all processors would likely require using something like process hacker to get things working in a optimal way with automation so e.g. affinity for svchost and browsers to e-cores and affinity for games to p-cores (good for security as well as e-cores dont have htt). Both of these schedule options still automatically favour the fastest two p-cores for single threaded cinebench which is nice, on my ryzen cpu's this doesnt happen. It also doesnt happen on my 9900k, a reason why I went to all core clock speed on 9900k. But my testing on ryzen and 9900k was done on 1809, whilst on the 13700k was on 21H2, so its possible 1809 has no programming for "favoured cores" as that was introduced later I think.

AMD of course have this problem as well, with some of their processors for different reasons.

I assume the improvements in Windows 11 are just a better default behaviour when specific cpu's are recognised. For better OOB experience.

- Joined

- Jun 24, 2015

- Messages

- 8,370 (2.28/day)

- Location

- Western Canada

| System Name | ab┃ob |

|---|---|

| Processor | 7800X3D┃5800X3D |

| Motherboard | B650E PG-ITX┃X570 Impact |

| Cooling | NH-U12A + T30┃AXP120-x67 |

| Memory | 64GB 6400CL32┃32GB 3600CL14 |

| Video Card(s) | RTX 4070 Ti Eagle┃RTX A2000 |

| Storage | 8TB of SSDs┃1TB SN550 |

| Case | Caselabs S3┃Lazer3D HT5 |

At least it's nice for them to finally have a real name. These Zen 4c cores are literally just APU grade Zen 4, jammed into a chiplet. Better than having to call them "reduced-cache Zen" every time to distinguish them.

Yes, much more capable than an E-core, but in heterogeneous applications it requires no less scheduling optimization. Half-cache Zen 2 and Zen 3 perform slightly worse per clock in productivity and significantly worse in games/cache heavy workloads.

A Zen4c does everything a zen4 does just probably a bit slower.

Yes, much more capable than an E-core, but in heterogeneous applications it requires no less scheduling optimization. Half-cache Zen 2 and Zen 3 perform slightly worse per clock in productivity and significantly worse in games/cache heavy workloads.

- Joined

- Oct 6, 2021

- Messages

- 1,979 (1.44/day)

| System Name | Raspberry Pi 7 Quantum @ Overclocked. |

|---|

It seems to me that the simplification of the design has the weakness of not reaching clocks as high as Zen4. But this is not a problem on CPUs intended for servers...

"The only thing that's changed is that the effective L3 cache per core has been reduced to 2 MB, from 4 MB on the 8-core "Zen 4" CCD."

If that's true why the slide says 35% smaller comparing just core+L2 ???

"The only thing that's changed is that the effective L3 cache per core has been reduced to 2 MB, from 4 MB on the 8-core "Zen 4" CCD."

If that's true why the slide says 35% smaller comparing just core+L2 ???

Last edited:

- Joined

- Feb 3, 2017

- Messages

- 4,017 (1.30/day)

| Processor | Ryzen 7800X3D |

|---|---|

| Motherboard | ROG STRIX B650E-F GAMING WIFI |

| Memory | 2x16GB G.Skill Flare X5 DDR5-6000 CL36 (F5-6000J3636F16GX2-FX5) |

| Video Card(s) | INNO3D GeForce RTX™ 4070 Ti SUPER TWIN X2 |

| Storage | 2TB Samsung 980 PRO, 4TB WD Black SN850X |

| Display(s) | 42" LG C2 OLED, 27" ASUS PG279Q |

| Case | Thermaltake Core P5 |

| Power Supply | Fractal Design Ion+ Platinum 760W |

| Mouse | Corsair Dark Core RGB Pro SE |

| Keyboard | Corsair K100 RGB |

| VR HMD | HTC Vive Cosmos |

at 35% smaller,

Unless it is very heavy clock deficit, there should be no reason for keeping plain old Zen4 around any more.So all that's left unknown is the effect on max boost clock's.

I don't think the enterprise version ever needed the high frequency capability that zen has so these probably cannot run as fast.

But it's intriguing.

- Joined

- Jan 24, 2011

- Messages

- 295 (0.06/day)

| Processor | AMD Ryzen 5900X |

|---|---|

| Motherboard | MSI MAG X570 Tomahawk |

| Cooling | Dual custom loops |

| Memory | 4x8GB G.SKILL Trident Z Neo 3200C14 B-Die |

| Video Card(s) | AMD Radeon RX 6800XT Reference |

| Storage | ADATA SX8200 480GB, Inland Premium 2TB, various HDDs |

| Display(s) | MSI MAG341CQ |

| Case | Meshify 2 XL |

| Audio Device(s) | Schiit Fulla 3 |

| Power Supply | Super Flower Leadex Titanium SE 1000W |

| Mouse | Glorious Model D |

| Keyboard | Drop CTRL, lubed and filmed Halo Trues |

Cache actually doesn't consume much energy, so it doesn't have a large effect on temps. The bigger contributor to lower temps will be the reduced clockspeed.Did you pull that from the 35% decrease in size, and just hoped the math is the same?

Cause uh, halving the cache likely decreases those quite a bit

- Joined

- Nov 26, 2021

- Messages

- 1,902 (1.44/day)

- Location

- Mississauga, Canada

| Processor | Ryzen 7 5700X |

|---|---|

| Motherboard | ASUS TUF Gaming X570-PRO (WiFi 6) |

| Cooling | Noctua NH-C14S (two fans) |

| Memory | 2x16GB DDR4 3200 |

| Video Card(s) | Reference Vega 64 |

| Storage | Intel 665p 1TB, WD Black SN850X 2TB, Crucial MX300 1TB SATA, Samsung 830 256 GB SATA |

| Display(s) | Nixeus NX-EDG27, and Samsung S23A700 |

| Case | Fractal Design R5 |

| Power Supply | Seasonic PRIME TITANIUM 850W |

| Mouse | Logitech |

| VR HMD | Oculus Rift |

| Software | Windows 11 Pro, and Ubuntu 20.04 |

Last week, TechPowerUp reported on an analysis by SemiAnalysis that went over how AMD made Zen 4c smaller. While it's behind a paywall, the first part covering the physical design is free to read. The core sans the L2 cache is 44% smaller, i.e. nearly half the size of a Zen 4 core. It's an impressive feat of physical design."The only thing that's changed is that the effective L3 cache per core has been reduced to 2 MB, from 4 MB on the 8-core "Zen 4" CCD."

If that's true why the slide says 35% smaller comparing just core+L2 ???

TLDR:

- reducing the number of timing critical regions to just 4 from well over 10 in Zen 4 as seen in the diagram below: this sacrifices clock speed for density

- a new SRAM bitcell developed by TSMC for memories outside L2. As a 6T design, it saves area compared to the usual 8T designs

- lower clock speed target allows denser circuits

- The L3 also lacks the arrays of Through-Silicon Vias (TSV) for 3D V-Cache, giving a small area saving. This means that there's no possibility of a stacked L3 cache for Zen 4c.

- Joined

- Oct 6, 2021

- Messages

- 1,979 (1.44/day)

| System Name | Raspberry Pi 7 Quantum @ Overclocked. |

|---|

Thank you, That is a much clearer and more detailed explanation. Zen4c would be a much better efficiency core if AMD decides to beat intel at its own game.Last week, TechPowerUp reported on an analysis by SemiAnalysis that went over how AMD made Zen 4c smaller. While it's behind a paywall, the first part covering the physical design is free to read. The core sans the L2 cache is 44% smaller, i.e. nearly half the size of a Zen 4 core. It's an impressive feat of physical design.

TLDR:

- reducing the number of timing critical regions to just 4 from well over 10 in Zen 4 as seen in the diagram below: this sacrifices clock speed for density

- a new SRAM bitcell developed by TSMC for memories outside L2. As a 6T design, it saves area compared to the usual 8T designs

- lower clock speed target allows denser circuits

- The L3 also lacks the arrays of Through-Silicon Vias (TSV) for 3D V-Cache, giving a small area saving. This means that there's no possibility of a stacked L3 cache for Zen 4c.

View attachment 300809

- Joined

- Jun 24, 2018

- Messages

- 58 (0.02/day)

- Location

- Chicago, IL

| System Name | Replicator |

|---|---|

| Processor | Ryzen 7 1700 |

| Motherboard | ROG Strix x470-i |

| Memory | G-Skill Trident Z Neo 32GB 3600 |

| Video Card(s) | ROG STRIX-GTX1080-O8G-GAMING |

It's kind of funny because people have brought into the marketing fluff when it comes to their desktop product stack. Efficiency cores are just as bloated as the Performance cores. Because they are using skylake architecture for those cores.It's all good, I just loathe intels E-cores because they used a name that is the exact opposite of the product to mislead people about them

They're more efficient at single threaded tasks, and then intel uses them exclusively for multi threaded tasks.

Just... Ugh.

- Joined

- Oct 27, 2009

- Messages

- 1,239 (0.22/day)

- Location

- Republic of Texas

| System Name | [H]arbringer |

|---|---|

| Processor | 4x 61XX ES @3.5Ghz (48cores) |

| Motherboard | SM GL |

| Cooling | 3x xspc rx360, rx240, 4x DT G34 snipers, D5 pump. |

| Memory | 16x gskill DDR3 1600 cas6 2gb |

| Video Card(s) | blah bigadv folder no gfx needed |

| Storage | 32GB Sammy SSD |

| Display(s) | headless |

| Case | Xigmatek Elysium (whats left of it) |

| Audio Device(s) | yawn |

| Power Supply | Antec 1200w HCP |

| Software | Ubuntu 10.10 |

| Benchmark Scores | http://valid.canardpc.com/show_oc.php?id=1780855 http://www.hwbot.org/submission/2158678 http://ww |

Architectural change that effects performance...It seems to me that the simplification of the design has the weakness of not reaching clocks as high as Zen4. But this is not a problem on CPUs intended for servers...

"The only thing that's changed is that the effective L3 cache per core has been reduced to 2 MB, from 4 MB on the 8-core "Zen 4" CCD."

If that's true why the slide says 35% smaller comparing just core+L2 ???

View attachment 300804

It has been power and density optimized allowing for 16 cores per ccx... this means 16 cores share the same cache that...8 shared before...

Now you get 128 core with 8 ccx/core chiplets vs 12 for 96 on zen4

I thought at one point AMD had slides to show that the "c" version would just be cache reduced but when it will be implemented on the consumer LITTLE.big side they will combine the prior generation "c" cores with the next generation "p" cores. I might be miss remembering or it was just a rumor because I can't find definitive information on this with a quick google.

If intel would need to use their server Xeon Phi atom cores they could get on "feature parity" with their "p" cores at least when it comes to hyperthreading and AVX-512. The ATOM cores would still be a heck of a lot slower.

ark.intel.com

ark.intel.com

If intel would need to use their server Xeon Phi atom cores they could get on "feature parity" with their "p" cores at least when it comes to hyperthreading and AVX-512. The ATOM cores would still be a heck of a lot slower.

Intel® Xeon Phi™ Processor 7235 (16GB, 1.3 GHz, 64 Core) - Product Specifications | Intel

Intel® Xeon Phi™ Processor 7235 (16GB, 1.3 GHz, 64 Core) quick reference with specifications, features, and technologies.

- Joined

- Nov 26, 2021

- Messages

- 1,902 (1.44/day)

- Location

- Mississauga, Canada

| Processor | Ryzen 7 5700X |

|---|---|

| Motherboard | ASUS TUF Gaming X570-PRO (WiFi 6) |

| Cooling | Noctua NH-C14S (two fans) |

| Memory | 2x16GB DDR4 3200 |

| Video Card(s) | Reference Vega 64 |

| Storage | Intel 665p 1TB, WD Black SN850X 2TB, Crucial MX300 1TB SATA, Samsung 830 256 GB SATA |

| Display(s) | Nixeus NX-EDG27, and Samsung S23A700 |

| Case | Fractal Design R5 |

| Power Supply | Seasonic PRIME TITANIUM 850W |

| Mouse | Logitech |

| VR HMD | Oculus Rift |

| Software | Windows 11 Pro, and Ubuntu 20.04 |

The Xeon Phi atom cores are much slower than the Gracemont cores used along side Golden Cove and Raptor Cove. Their only saving grace is AVX-512.If intel would need to use their server Xeon Phi atom cores they could get on "feature parity" with their "p" cores at least when it comes to hyperthreading and AVX-512. The ATOM cores would still be a heck of a lot slower.

Intel® Xeon Phi™ Processor 7235 (16GB, 1.3 GHz, 64 Core) - Product Specifications | Intel

Intel® Xeon Phi™ Processor 7235 (16GB, 1.3 GHz, 64 Core) quick reference with specifications, features, and technologies.ark.intel.com

- Joined

- Oct 28, 2012

- Messages

- 1,493 (0.32/day)

| Processor | AMD Ryzen 3700x |

|---|---|

| Motherboard | asus ROG Strix B-350I Gaming |

| Cooling | Deepcool LS520 SE |

| Memory | crucial ballistix 32Gb DDR4 |

| Video Card(s) | RTX 3070 FE |

| Storage | WD sn550 1To/WD ssd sata 1To /WD black sn750 1To/Seagate 2To/WD book 4 To back-up |

| Display(s) | LG GL850 |

| Case | Dan A4 H2O |

| Audio Device(s) | sennheiser HD58X |

| Power Supply | Corsair SF600 |

| Mouse | MX master 3 |

| Keyboard | Master Key Mx |

| Software | win 11 pro |

Looking at how Sapphire rapids struggle againt zen3 TR at equal core count while using more power, I'm really not surprised that they are being used in that manner. If RPL is already digusting when it comes to power draw, A 16 P-core i9 might have been uglier to witness on conssumers platforms. A 65w locked 7950x is still faster than golden cove going at 200 watts. (Note that Puget is enforcing PL1 125w and PL2 253w on the core i9 since those are the reference value set by Intel, and it's still faster than the xeon)It's all good, I just loathe intels E-cores because they used a name that is the exact opposite of the product to mislead people about them

They're more efficient at single threaded tasks, and then intel uses them exclusively for multi threaded tasks.

Just... Ugh.

- Joined

- Nov 3, 2011

- Messages

- 701 (0.14/day)

- Location

- Australia

| System Name | Eula |

|---|---|

| Processor | AMD Ryzen 9 7950X |

| Motherboard | MSI MPG B850 Edge Ti WiFi |

| Cooling | Corsair H150i Elite LCD XT White |

| Memory | Trident Z5 Neo RGB DDR5-6000 CL32-38-38-96 1.40V 64GB (2x32GB) AMD EXPO F5-6000J3238G32GX2-TZ5NR |

| Video Card(s) | Gigabyte GeForce RTX 4080 GAMING OC |

| Storage | Crucial P3 Plus, 4 TB NVMe, Samsung 980 Pro 2TB NVMe, Toshiba N300 10TB HDD, WDC Red Pro NAS HDD |

| Display(s) | Acer Predator X32FP 32in 160Hz 4K, Corsair Xeneon 32UHD144 32in 144 hz 4K |

| Case | Antec Constellation C8 RGB White |

| Audio Device(s) | Creative Sound Blaster Z |

| Power Supply | Corsair HX1000 Platinum 1000W |

| Mouse | SteelSeries Prime Pro Gaming Mouse |

| Keyboard | SteelSeries Apex 5 |

| Software | MS Windows 11 Pro |

Apple's and orange's, there is a bigger gap between the e cores and p then this.

E cores are single threaded and have fewer resources and less capability And a reduced ISA no AVX for example.

So yes Intel do smaller but they are also weaker less capable and actually require process scheduler interaction.

A Zen4c does everything a zen4 does just probably a bit slower.

Intel's E-Cores has AVX2 via three 128-bit SIMD units, hence they are closer to AMD's Zen 1.x's quad 128-bit SIMD units.

Intel's E-Cores do not have AVX-512.

The point is they could bolt on HT and AVX-512 as they have before and they have the "roadmap" on how to do it in the next version if they wanted. Being Intel they won't until they are forced too by AMD.The Xeon Phi atom cores are much slower than the Gracemont cores used along side Golden Cove and Raptor Cove. Their only saving grace is AVX-512.

- Joined

- Nov 3, 2011

- Messages

- 701 (0.14/day)

- Location

- Australia

| System Name | Eula |

|---|---|

| Processor | AMD Ryzen 9 7950X |

| Motherboard | MSI MPG B850 Edge Ti WiFi |

| Cooling | Corsair H150i Elite LCD XT White |

| Memory | Trident Z5 Neo RGB DDR5-6000 CL32-38-38-96 1.40V 64GB (2x32GB) AMD EXPO F5-6000J3238G32GX2-TZ5NR |

| Video Card(s) | Gigabyte GeForce RTX 4080 GAMING OC |

| Storage | Crucial P3 Plus, 4 TB NVMe, Samsung 980 Pro 2TB NVMe, Toshiba N300 10TB HDD, WDC Red Pro NAS HDD |

| Display(s) | Acer Predator X32FP 32in 160Hz 4K, Corsair Xeneon 32UHD144 32in 144 hz 4K |

| Case | Antec Constellation C8 RGB White |

| Audio Device(s) | Creative Sound Blaster Z |

| Power Supply | Corsair HX1000 Platinum 1000W |

| Mouse | SteelSeries Prime Pro Gaming Mouse |

| Keyboard | SteelSeries Apex 5 |

| Software | MS Windows 11 Pro |

Looking at how Sapphire rapids struggle againt zen3 TR at equal core count while using more power, I'm really not surprised that they are being used in that manner. If RPL is already digusting when it comes to power draw, A 16 P-core i9 might have been uglier to witness on conssumers platforms. A 65w locked 7950x is still faster than golden cove going at 200 watts. (Note that Puget is enforcing PL1 125w and PL2 253w on the core i9 since those are the reference value set by Intel, and it's still faster than the xeon)

View attachment 300823View attachment 300824

Cinebench R23 doesn't use AVX-512.

Are you using Cinema 4D R25 or Blender 3.x?

-------------------

After 10 minute run, Intel Core i9 13900KS's scores are lower.

Last edited:

- Joined

- Aug 21, 2013

- Messages

- 2,207 (0.51/day)

- Location

- Estonia

| System Name | DarkStar |

|---|---|

| Processor | AMD Ryzen 7 5800X3D |

| Motherboard | Gigabyte X570 Aorus Master 1.0 (BIOS F39g) |

| Cooling | Arctic Liquid Freezer II 420mm AIO (rev4) |

| Memory | 4x8GB Patriot Viper DDR4 4400C19 @ 3733Mhz 14-14-13-27 1T |

| Video Card(s) | Gigabyte Radeon RX 9070 XT Gaming OC 16GB GDDR6 @ 3400Mhz Core/22Gbps Mem |

| Storage | 1TB Samsung 990 Pro (OS);2TB Samsung PM9A1;4TB XPG S70 Blade (Games);14TB WD UltraStar HC530 (Video) |

| Display(s) | 27" LG UltraGear 27GS85Q-B @ 2560x1440 @ 200Hz, Nano-IPS |

| Case | be quiet! Dark Base Pro 900 Rev.2 |

| Audio Device(s) | SteelSeries Arctis Nova Pro Wireless |

| Power Supply | 1000W Seasonic PRIME Ultra Titanium;600W APC SMT750i UPS |

| Mouse | Logitech G604 |

| Keyboard | Logitech G910 Orion Spark |

| Software | Windows 11 Pro x64 24H2 (Build 26100.4351) |

Still one as 4c is ~35% smaller. In order to pack two 4c cores in the same area 4c would need to be half the size as regular 4.Intel can pack 4 E-Cores in the same size as 1 P-Core. What about AMD? How many Zen4c cores for one Zen 4 core?

However i could see a possible two chiplet AM5 version where one chiplet uses 8 Zen 4 cores and another uses 16 Zen 4c cores giving a total of 24c/48t albeit with a reduced total L3 compared to 7950X (and 7950X3D).

Not sure there is market for such a chip as it would be multi-threaded focused product that would likely suffer the same or worse problems in games as 7950X does and would lose to X3D parts for sure. However there is an argument to be made that a regular 7950X could be replaced by this with small performance hit in cache sensitive workloads. Because 7950X buyers likely care more about core counts rather than cache.

Also im not sure if it's viable to make a model that has two chiplets with different core counts because correct me if im wrong but thus far all AMD models that have used two chiplets have used the same core counts on each chiplet?

- Joined

- Oct 28, 2012

- Messages

- 1,493 (0.32/day)

| Processor | AMD Ryzen 3700x |

|---|---|

| Motherboard | asus ROG Strix B-350I Gaming |

| Cooling | Deepcool LS520 SE |

| Memory | crucial ballistix 32Gb DDR4 |

| Video Card(s) | RTX 3070 FE |

| Storage | WD sn550 1To/WD ssd sata 1To /WD black sn750 1To/Seagate 2To/WD book 4 To back-up |

| Display(s) | LG GL850 |

| Case | Dan A4 H2O |

| Audio Device(s) | sennheiser HD58X |

| Power Supply | Corsair SF600 |

| Mouse | MX master 3 |

| Keyboard | Master Key Mx |

| Software | win 11 pro |

I'm using a mix of both, but the point that I was trying to make is that the e-core are being used for MT on the conssumer platform because a 16 P-core i9 wouldn't have been competitive against Ryzen, especially with intel 7 having to carry intel until late 2024.Cinebench R23 doesn't use AVX-512.

View attachment 300826

View attachment 300827

View attachment 300828

Are you using Cinema 4D R25 or Blender 3.x?

-------------------

View attachment 300829

After 10 minute run, Intel Core i9 13900KS's scores are lower.

The e-cores are not just marketing, It's literally what allows Intel to stay relevant on the conssumer side for people who are not just gaming. Them lacking AVX512 isn't ideal, but it's either that, or let the competition take the performance and efficiency crown across the board

- Joined

- Feb 1, 2019

- Messages

- 4,053 (1.72/day)

- Location

- UK, Midlands

| System Name | Main PC |

|---|---|

| Processor | 13700k |

| Motherboard | Asrock Z690 Steel Legend D4 - Bios 13.02 |

| Cooling | Noctua NH-D15S |

| Memory | 32 Gig 3200CL14 |

| Video Card(s) | 4080 RTX SUPER FE 16G |

| Storage | 1TB 980 PRO, 2TB SN850X, 2TB DC P4600, 1TB 860 EVO, 4TB WD SA510, 2x 3TB WD Red, 1x 4TB WD Red |

| Display(s) | LG 27GL850 |

| Case | Fractal Define R4 |

| Audio Device(s) | Soundblaster AE-9 |

| Power Supply | Antec HCG 750 Gold |

| Software | Windows 10 21H2 LTSC |

Looking at the posts in the thread, lower clocks and no 3d cache.So what is the catch?

That is absolutely fine for server type usage.

Yep the e-cores are keeping intel in the game on production type workloads, like software encoding, compressing, and compiling software. So absolutely used to keep multithreading competitive with AMD.I'm using a mix of both, but the point that I was trying to make is that the e-core are being used for MT on the conssumer platform because a 16 P-core i9 wouldn't have been competitive against Ryzen, especially with intel 7 having to carry intel until late 2024.

The e-cores are not just marketing, It's literally what allows Intel to stay relevant on the conssumer side for people who are not just gaming. Them lacking AVX512 isn't ideal, but it's either that, or let the competition take the performance and efficiency crown across the board

The p-cores keep them ahead on typical consumer use like gaming, office apps, web browsing, media playback.

Absolutely fine for regular desktops as well, I'd rather get a 5GHz chip with 10% less ST performance than 7950x & 50-100% more cores. I bet if they decided to release a full lineup they could wipe Intel clean across lots of segments with their massive price & (MT) performance advantage! The catch for consumers though is that they make less through desktops so they won't concentrate on this for probably at least half a year.That is absolutely fine for server type usage.

- Joined

- Mar 10, 2010

- Messages

- 11,880 (2.12/day)

- Location

- Manchester uk

| System Name | RyzenGtEvo/ Asus strix scar II |

|---|---|

| Processor | Amd R5 5900X/ Intel 8750H |

| Motherboard | Crosshair hero8 impact/Asus |

| Cooling | 360EK extreme rad+ 360$EK slim all push, cpu ek suprim Gpu full cover all EK |

| Memory | Gskill Trident Z 3900cas18 32Gb in four sticks./16Gb/16GB |

| Video Card(s) | Asus tuf RX7900XT /Rtx 2060 |

| Storage | Silicon power 2TB nvme/8Tb external/1Tb samsung Evo nvme 2Tb sata ssd/1Tb nvme |

| Display(s) | Samsung UAE28"850R 4k freesync.dell shiter |

| Case | Lianli 011 dynamic/strix scar2 |

| Audio Device(s) | Xfi creative 7.1 on board ,Yamaha dts av setup, corsair void pro headset |

| Power Supply | corsair 1200Hxi/Asus stock |

| Mouse | Roccat Kova/ Logitech G wireless |

| Keyboard | Roccat Aimo 120 |

| VR HMD | Oculus rift |

| Software | Win 10 Pro |

| Benchmark Scores | laptop Timespy 6506 |

Didn't know that.Intel's E-Cores has AVX2 via three 128-bit SIMD units, hence they are closer to AMD's Zen 1.x's quad 128-bit SIMD units.

Intel's E-Cores do not have AVX-512.

It is true that those are small enough, but the main issue with Atom e-cores is that those cores do not support hyper-threading and AVX512, which is one of reasons there was a complete mess with AVX512 on Alder Lake and Raptor Lake CPU. Hence, Intel nerfed AVX512 and owners cannot benefit from it.Intel can pack 4 E-Cores in the same size as 1 P-Core. What about AMD? How many Zen4c cores for one Zen 4 core?

Zen4 c-cores are fully capable cores with smaller L3 cache. c-cores support HT and AVX512 workloads; perfect for cloud.

So, Sierra Forest CPU next year will have 144 Atom cores: 144C/114T. Bergamo CPU has 128C/256T. It's a monster chip for cloud computing, trumping both Intel and ARM solutions by several times, while easily slotted in the same socket 6096. Data centre partners will not need to buy new server motherboads either.

Next year, Turin Zen5 c-cores should bring another evolution in design in 16-core chiplets, namely current two 8-core CCX will be unified into 16-core CCX/CCD. If they want to increase core count to 192 c-cores, they will have to change packaging and I/O in order to place additional two chiplets, as there is no space left on current package due to communication pathways. That's why 16-core chiplets on Bergamo are placed apart and not jointly near each other.

Last edited:

- Joined

- Nov 26, 2021

- Messages

- 1,902 (1.44/day)

- Location

- Mississauga, Canada

| Processor | Ryzen 7 5700X |

|---|---|

| Motherboard | ASUS TUF Gaming X570-PRO (WiFi 6) |

| Cooling | Noctua NH-C14S (two fans) |

| Memory | 2x16GB DDR4 3200 |

| Video Card(s) | Reference Vega 64 |

| Storage | Intel 665p 1TB, WD Black SN850X 2TB, Crucial MX300 1TB SATA, Samsung 830 256 GB SATA |

| Display(s) | Nixeus NX-EDG27, and Samsung S23A700 |

| Case | Fractal Design R5 |

| Power Supply | Seasonic PRIME TITANIUM 850W |

| Mouse | Logitech |

| VR HMD | Oculus Rift |

| Software | Windows 11 Pro, and Ubuntu 20.04 |

As with the P cores, Intel has clocked the E cores too high. Clocking them closer to 3 Ghz would make them true E cores: more efficient than P cores. Chips and Cheese found Gracemont to be more efficient than Golden Cove at a variety of tasks if clock speeds were kept in check. Notably, these more efficient clock speeds were lower than Intel's default for the 12900k.Yep the e-cores are keeping intel in the game on production type workloads, like software encoding, compressing, and compiling software. So absolutely used to keep multithreading competitive with AMD.