Intel Apparently Reusing Iris Branding for Xe Integrated Graphics; Tiger Lake With 768 Shading Units Spotted

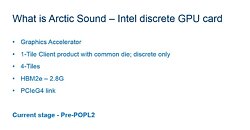

Another day, another Intel Tiger Lake and Xe graphics leak. This time, it comes courtesy of secret benchmark spotter extraordinaire TUM_APISAK, who spotted an Intel Tiger Lake CPU with integrated graphics on SiSoftware. Tiger Lake will ship with a graphics capability that reaches at least 96 Execution units (which boils down to the referred 768 Shading Units), which corresponds to the graphics prowess available on Intel's (currently discrete) DG1-SDV. The Iris Xe graphics on this benchmark are running at 1.3 GHz, with a 6.3 GB of memory on their elbow.