Friday, April 6th 2018

Intel Could Develop its own big.LITTLE x86 Adaptation

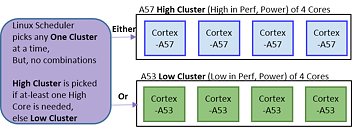

big.LITTLE is an innovation by ARM, which seeks to minimize power-draw on mobile devices. It is a sort of heterogeneous multi-core CPU design, in which a few "big" high-performance CPU cores work alongside a few extremely low-power "little" CPU cores. The idea here is that the low-power cores consume much lesser power at max load, than the high-performance cores at their minimum power-state, so the high-performance cores can be power-gated when the system doesn't need them (i.e. most of the time).

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

Source:

Ashraf Eassa (Twitter)

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

36 Comments on Intel Could Develop its own big.LITTLE x86 Adaptation

2 ICL Cores

3 TNT Cores

My 0.2 cents~

Also, the SD835 already uses big.LITTLE, so perhaps the Windows scheduler is already ready for an Intel version?

This could turn up to be interesting, H-series cores (35W) mixed with regular cores (65W).

As for Kernel rework, the logic should be there, since both Linux and Windows knows what ARM cores are.

Only the integration of Atoms power management of C-States into the Core series...

Maybe you should release another roadmap, so we understand what you really want to do now.

The most profitable phone makers are all vertically integrated players like Apple, Samsung, Huawei with the possible exception of BBK electronics & Xiaomi, who have a very low cost base & get by largely using viral marketing & flash sales.

Also a touch of irony here as Intel(?) & many other enthusiasts derided big little as a joke & basically laughed at the idea of many cores in a mobile, a tonne of irony I'd say.

two or maybe one low power core could easily prop up stand by , and in some cases media use ,making systems more battery friendly.

It's definitely a nightmare but it can work, provided the scheduler prevents a program from jumping to big/little cores which lack specific instructions sets. A number of programs will also need to be updated so that they don't crash the system, doing the switch.

There were some serious growing pains with it. Not to mention the ISA issues mentioned above.

Frankly, I don't see intel handling this well. I think this is something we should view with skepticism rather than embrace.

Edit: Think about Ryzen: besides some scheduling tweaks in Windows, no software needed updates to work fine with AMD's CCX design. And even then AMD stated Windows' schduler was pretty much fine already.

Definitely interesting to see where this leads up to, also what comes after Goldmont Plus & whether Atom will ever get parity with Core.