1

Cores

1

Threads

33 W

TDP

1300 MHz

Frequency

N/A

Boost

Tualatin

Codename

Socket 370

Socket

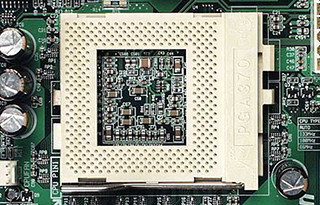

Intel Socket 370

The Intel Celeron 1300 was a desktop processor with 1 core, launched in January 2002, at an MSRP of $118. It is part of the Celeron lineup, using the Tualatin architecture with Socket 370. Celeron 1300 has 256 KB of L2 cache and operates at 1300 MHz. Intel is making the Celeron 1300 on a 130 nm production node using 44 million transistors. The multiplier is locked on Celeron 1300, which limits its overclocking potential.

With a TDP of 33 W, the Celeron 1300 consumes only little energy. The highest officially supported memory speed is 133 MT/s, but with overclocking (and the right memory modules) you can go even higher. Actual memory technology support depends on the chosen motherboard, because the memory controller is located on the motherboard (not in the processor). Although the processor doesn't come with integrated graphics, certain motherboards with compatible chipsets can provide this capability.

Many games will refuse to start on this processor due to the lack of the SSE2/SSE3/SSE4 instruction set.

With a TDP of 33 W, the Celeron 1300 consumes only little energy. The highest officially supported memory speed is 133 MT/s, but with overclocking (and the right memory modules) you can go even higher. Actual memory technology support depends on the chosen motherboard, because the memory controller is located on the motherboard (not in the processor). Although the processor doesn't come with integrated graphics, certain motherboards with compatible chipsets can provide this capability.

Many games will refuse to start on this processor due to the lack of the SSE2/SSE3/SSE4 instruction set.

Physical

| Socket: | Intel Socket 370 |

|---|---|

| Foundry: | Intel |

| Process Size: | 130 nm |

| Transistors: | 44 million |

| Die Size: | 80 mm² |

| Package: | µPGA |

| tCaseMax: | 70°C |

Processor

| Market: | Desktop |

|---|---|

| Production Status: | End-of-life |

| Release Date: | Jan 3rd, 2002 |

| Launch Price: | $118 |

| Part#: | SL5VR SL5ZJ SL6C7 SL6JT |

Performance

| Frequency: | 1300 MHz |

|---|---|

| Turbo Clock: | N/A |

| Base Clock: | 100 MHz |

| Multiplier: | 13.0x |

| Multiplier Unlocked: | No |

| Voltage: | 1.5 V |

| TDP: | 33 W |

Architecture

| Codename: | Tualatin |

|---|---|

| Generation: |

Celeron

(Tualatin) |

| Memory Support: |

unknown

Depends on motherboard |

| Rated Speed: | 133 MT/s |

| Memory Bus: | Single-channel |

| Northbridge Location: | Motherboard |

| ECC Memory: | No |

| Chipsets: | i815, i815e, VIA 694T, ALi M1651T, SiS 635T |

Core Config

| # of Cores: | 1 |

|---|---|

| # of Threads: | 1 |

| SMP # CPUs: | 1 |

| Integrated Graphics: | On certain motherboards (Chipset feature) |

Cache

| Cache L1: | 32 KB |

|---|---|

| Cache L2: | 256 KB |

Features

|

Notes

| Many S-Specs overlap in stepping code. Stepping table is as follows: Stepping A0 - SL5VR, SL5ZJ, SL6JT Stepping A3 - SL5VR Stepping B1 - SL6C7, SL6JT Stepping BA - SL6C7 |

Jun 15th, 2024 17:52 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- when using only 2 out of 4 ram slots which 2 are best? (2)

- Post your Speedometer 3.0 Score (46)

- Intel Optane 1TB (14)

- Amazing moderator acknowledgement (9)

- Can you help me decide for which AM4 CPU to buy plz? (18)

- new tv/display what one? what to avoid? (23)

- System shutdown from short when connecting USB type C cable? (20)

- LOL ASUS says this is $200 in repair, Steve from gamers Nexus smokes ASUS, Steam Deck til I die boys!!!! (151)

- A Final Fantasy IX Reminiscence - My love letter and homage to one of the best stories ever told (0)

- I should upgrade my gpu and psu? (10)

Popular Reviews

- Aune AR5000 Headphones + S17 Pro Headphones Amplifier Review

- Pulsar Xlite V3 eS Review

- VAXEE Outset AX Wireless (4K) Review

- Upcoming Hardware Launches 2024 (Updated May 2024)

- Team Group T-Force G70 Pro 2 TB Review

- Intel Lunar Lake Technical Deep Dive - So many Revolutions in One Chip

- AMD Ryzen 7 7800X3D Review - The Best Gaming CPU

- NZXT H6 Flow RGB Review

- Quick Look: Final UX2000 Wireless Noise Canceling Headphones

- Thermal Grizzly KryoSheet Review - Tested on RX 7900 XTX with 475 W

Controversial News Posts

- Possible Specs of NVIDIA GeForce "Blackwell" GPU Lineup Leaked (132)

- NVIDIA RTX 5090 "Blackwell" Founders Edition to Implement the "RTX 4090 Ti" Cinderblock Design (118)

- AMD Outs Ryzen 5000XT Processors for Socket AM4, an 8-year Old Socket (105)

- Nightmare Fuel for Intel: Arm CEO Predicts Arm will Take Over 50% Windows PC Market-share by 2029 (105)

- AMD Ryzen 9000 Zen 5 Single Thread Performance at 5.80 GHz Found 19% Over Zen 4 (103)

- AMD Says Ryzen 9000 Series Won't Beat 7000X3D Series at Gaming (101)

- AMD Zen 5 Storms into Gaming Desktops with Ryzen 9000 "Granite Ridge" Processors (100)

- Biden Administration to Revive Trump-Era Tariffs on China-made GPUs and Motherboards (95)