Intel to Tease Core Ultra "Arrow Lake" at Computex?

Intel is rumored to be preparing to tease its Core Ultra 2-series "Arrow Lake" processor at the 2024 Computex, which gets underway this June. The series itself isn't expected to launch before Q4-2024, but Computex is the only major global event between June and January for Intel to unveil or tease its next-generation processor, so here we are. At this point we don't know which exact platform of "Arrow Lake" Intel is planning to tease—whether these are the mobile variants, or the Socket LGA1851 desktop "Arrow Lake-S." An unveiling of the latter would almost definitely entail PC motherboard vendors being allowed to show off their first compatible motherboards at Computex—the perfect platform for them to do so.

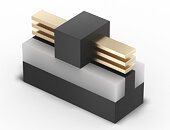

The Core Ultra "Arrow Lake" retains a Foveros Tiled (chiplet) construction of "Meteor Lake," but with advancements to the chip's Compute tile, which is built on the Intel 20A foundry node, and rocks new "Lion Cove" P-cores and "Skymont" E-cores; an updated I/O tile, and an iGPU based on the updated Xe-LPG+ graphics architecture. Since the processor now serves practically all PCH functions, the mobile "Arrow Lake" is a single-chip solution, whereas the desktop "Arrow Lake-S" is expected to remain 2-chip. There will be more I/O from the CPU, though, which is why the socket has 151 more pins than the LGA1700.

The Core Ultra "Arrow Lake" retains a Foveros Tiled (chiplet) construction of "Meteor Lake," but with advancements to the chip's Compute tile, which is built on the Intel 20A foundry node, and rocks new "Lion Cove" P-cores and "Skymont" E-cores; an updated I/O tile, and an iGPU based on the updated Xe-LPG+ graphics architecture. Since the processor now serves practically all PCH functions, the mobile "Arrow Lake" is a single-chip solution, whereas the desktop "Arrow Lake-S" is expected to remain 2-chip. There will be more I/O from the CPU, though, which is why the socket has 151 more pins than the LGA1700.