Kioxia Develops New 3D Semicircular Flash Memory Cell Structure "Twin BiCS FLASH"

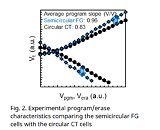

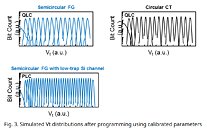

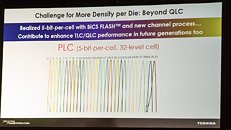

Kioxia Corporation today announced the development of the world's first three-dimensional (3D) semicircular split-gate flash memory cell structure "Twin BiCS FLASH" using specially designed semicircular Floating Gate (FG) cells. Twin BiCS FLASH achieves superior program slope and a larger program/erase window at a much smaller cell size compared to conventional circular Charge Trap (CT) cells. These attributes make this new cell design a promising candidate to surpass four bits per cell (QLC) for significantly higher memory density and fewer stacking layers. This technology was announced at the IEEE International Electron Devices Meeting (IEDM) held in San Francisco, CA on December 11th.

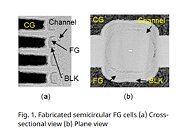

3D flash memory technology has achieved high bit density with low cost per bit by increasing the number of cell stacked layers as well as by implementing multilayer stack deposition and high aspect ratio etching. In recent years, as the number of cell layers exceeds 100, managing the trade-offs among etch profile control, size uniformity and productivity is becoming increasingly challenging. To overcome this problem, Kioxia developed a new semicircular cell design by splitting the gate electrode in the conventional circular cell to reduce cell size compared to the conventional circular cell, enabling higher-density memory at a lower number of cell layers.

3D flash memory technology has achieved high bit density with low cost per bit by increasing the number of cell stacked layers as well as by implementing multilayer stack deposition and high aspect ratio etching. In recent years, as the number of cell layers exceeds 100, managing the trade-offs among etch profile control, size uniformity and productivity is becoming increasingly challenging. To overcome this problem, Kioxia developed a new semicircular cell design by splitting the gate electrode in the conventional circular cell to reduce cell size compared to the conventional circular cell, enabling higher-density memory at a lower number of cell layers.