MSI AMD 500, 400, 300-series Motherboards Ready to Support Ryzen 5000/4000 Series

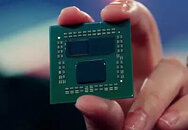

AMD recently announced the latest "Zen 3" and "Zen 2" new processors are coming to the market very soon for DIY users, which includes the ground-breaking AMD 3D V-Cache technology processor, the AMD Ryzen 7 5800X3D. Moreover, the mainstream Ryzen 7 5700X, Ryzen 5 5600, Ryzen 5 5500, Ryzen 5 4600G, Ryzen 5 4500, and Ryzen 3 4100 are all here for different levels of system builds.

MSI is committed to deliver gamers and creators the best experiences. This is why BIOS update is always great for most users. The latest AMD AGESA COMBO PI V2 1.2.0.6c BIOS was released for some MSI 500- and 400-series motherboards. The purpose of AGESA 1.2.0.6c is not only for better compatibility but also for maximizing AMD Ryzen 7 5800X3D performance. For the older 300-series motherboards, we will release the AGESA COMBO PI V2 1.2.0.6c beta BIOS by the end of April. Please refer to the following chart for more information.

MSI is committed to deliver gamers and creators the best experiences. This is why BIOS update is always great for most users. The latest AMD AGESA COMBO PI V2 1.2.0.6c BIOS was released for some MSI 500- and 400-series motherboards. The purpose of AGESA 1.2.0.6c is not only for better compatibility but also for maximizing AMD Ryzen 7 5800X3D performance. For the older 300-series motherboards, we will release the AGESA COMBO PI V2 1.2.0.6c beta BIOS by the end of April. Please refer to the following chart for more information.