Monday, January 11th 2021

Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

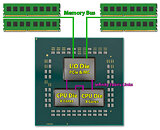

Certain AMD Ryzen 5 5600X and Ryzen 7 5800X processors are physically based on a dual-CCD design, according to an investigative report by Igor's Lab and Yuri "1usmus" Bubliy. The 5600X and 5800X are normally meant to be single-CCD processors owing to their core-counts. Based on the "Vermeer" multi-chip module design, the Ryzen 5000 series desktop processors use up to two 8-core CCDs to achieve their core-counts of up to 16 cores, with the 6-core 5600X and 8-core 5800X normally having just one CCD; while the 12-core 5900X and 16-core 5950X use two.

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

Source:

Igor's Lab

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

62 Comments on Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

I always wanted a socket AM3 system, something about the customizeability always appealed to me.

The Op States the extra CCD is dark silicon, dead to the world.

Although this isn't impossible it's unlikely.

Lasering never stopped us. There was the pencil trick, and later the "short these two CPU pins with a bit of copper in the socket" tricks back in the day.

But ... cores aside, wouldn't it be nice if one could at least activate the L3 cache on the second chip?

I don't think AMD has any incentive to do stuff like this any more. For the old Athlon X3s, I don't think they saw any value in going to the extra expense of actually lasering off the extra cores, and the proportion of users actually unlocking anything was probably small enough to not make a difference. These days, when PC gaming has blown up and DIY PC builds are suddenly the realm of even the cool kids? Not worth the inevitable RMA hassle of people breaking their CPUs and blaming AMD for "not supporting" "features" that are at best hacks. The more time passes, the more locked-down the hardware capabilities of PCs become.

Actually the 3950X numbers from the review you linked are really interesting, as there's no difference in latency between CCXes on the same chiplet or across them, which would suggest that either Infinity Fabric between each die has next to no latency compared to on-die IF, or that on-die CCX-to-CCX communication goes through the IOD or something similar. The latter sounds very inefficient, and the former sounds utopian, so I wonder what's the explanation there...

E.g my generation one Ryzen 5 1600 with dual channel 2666mhz ram benches at 50GB/s memory transfer rate ~ in AIDA and shows higher than expected bench in others too. Only when I overclock it on the fly using the original version of Ryzen Master. That should be impossible, theoretical max bandwidth with only 2 channels of this ram is 21.3 x 2=42.6GB.

I had wondered if there was either a bug in the benches or if that version of Ryzen Master accidentally has some code AMD should have taken out of it...