Rambus Expands Chipset for Advanced Data Center Memory Modules with DDR5 Server PMICs

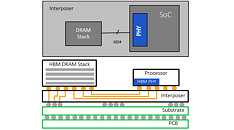

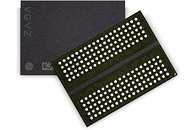

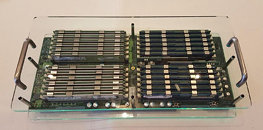

Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the availability of its new family of state-of-the-art DDR5 server Power Management ICs (PMICs), including an industry-leading extreme current device for high-performance applications. With this new family of server PMICs, Rambus offers module manufacturers a complete DDR5 RDIMM memory interface chipset supporting a broad range of data center use cases.

"Advanced data center workloads like generative AI require the highest bandwidth and capacity server RDIMMs tailored to meet ever-increasing memory needs of a growing data pipeline," said Sean Fan, chief operating officer at Rambus. "With the addition of this new family of server PMICs, we expand our foundational technology and offer customers a comprehensive memory interface chipset that supports multiple DDR5 server platform generations."

"Advanced data center workloads like generative AI require the highest bandwidth and capacity server RDIMMs tailored to meet ever-increasing memory needs of a growing data pipeline," said Sean Fan, chief operating officer at Rambus. "With the addition of this new family of server PMICs, we expand our foundational technology and offer customers a comprehensive memory interface chipset that supports multiple DDR5 server platform generations."