Intel Arrow Lake-HX Interposer Appears Online

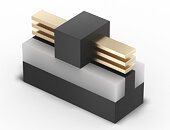

The Intel Design tools webpage has this week once again provided an early preview of upcoming processors - following on from an LGA1851-MTL-S CPU interposer appearing on the site late last month - indicating that a Meteor Lake-S desktop CPU range was due at some point later in 2023. Intel's latest webpage entry features the "BGA2114-ARL-HX Interposer for the Gen 5 VR Test Tool" with an SKU code that reads: "Q6B2114ARLHX."

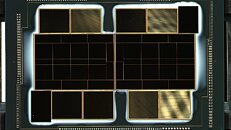

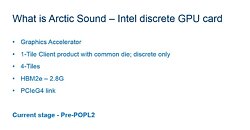

The BGA 2114 design points to a mobile processor platform, and industry analysts are fairly certain that Intel is preparing next generation high-end laptop CPUs in the form of its rumored Arrow Lake-HX lineup. This range is set to succeed the 13th generation Core-HX Raptor Lake family of mobile processors. The new BGA package looks to be slightly larger than the closest predecessor, possibly accommodating Intel's new "disaggregated" tile-based (tile is their term for chiplet) internal layout.

The BGA 2114 design points to a mobile processor platform, and industry analysts are fairly certain that Intel is preparing next generation high-end laptop CPUs in the form of its rumored Arrow Lake-HX lineup. This range is set to succeed the 13th generation Core-HX Raptor Lake family of mobile processors. The new BGA package looks to be slightly larger than the closest predecessor, possibly accommodating Intel's new "disaggregated" tile-based (tile is their term for chiplet) internal layout.