Intel "Sapphire Rapids" Xeon Processors Use "Golden Cove" CPU Cores, Company Clarifies in Linux Kernel Dev E-Mail Chain

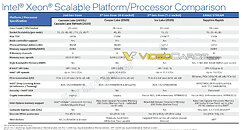

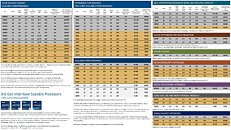

Intel's upcoming Xeon "Sapphire Rapids" processors which debut in the second half of 2021, will feature up to 80 "Golden Cove" CPU cores, and not the previously rumored "Willow Cove." This was clarified by an Intel developer in a Linux Kernel code e-mail chain. "Golden Cove" CPU cores are more advanced than the "Willow Cove" cores found in current-generation Intel products, such as the client "Tiger Lake" processors. Intel stated that "Golden Cove" introduces an IPC gain over "Willow Cove" (expressed as "ST perf"), increased AI inference performance from an updated GNI component, "network and 5G perf," which is possibly some form of network stack acceleration, and additional security features.

Over in the client segment, the 12th Gen Core "Alder Lake" processor debuts a client variant of "Golden Cove." The "Alder Lake-S" silicon features eight "Golden Cove" cores serving as the "big" performance cores, next to eight "little" low-power "Gracemont" cores. The client- and server implementations of "Golden Cove" could differ mainly in the ISA, with the client chip receiving a slightly skimmed AVX-512 and DLBoost instruction-sets, with only client-relevant instructions. The server variant, in addition being optimized for a high core-count multi-core topology; could feature a more substantial AVX-512 and DLBoost implementation relevant for HPC use-cases.

Over in the client segment, the 12th Gen Core "Alder Lake" processor debuts a client variant of "Golden Cove." The "Alder Lake-S" silicon features eight "Golden Cove" cores serving as the "big" performance cores, next to eight "little" low-power "Gracemont" cores. The client- and server implementations of "Golden Cove" could differ mainly in the ISA, with the client chip receiving a slightly skimmed AVX-512 and DLBoost instruction-sets, with only client-relevant instructions. The server variant, in addition being optimized for a high core-count multi-core topology; could feature a more substantial AVX-512 and DLBoost implementation relevant for HPC use-cases.