GIGABYTE Launches New G5/G7 Gaming Laptop

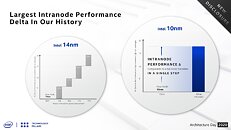

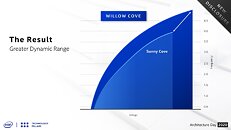

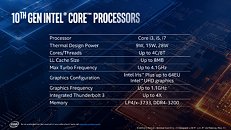

GIGABYTE TECHNOLOGY Co. Ltd, the global leading brand of PC, launches GIGABYTE Gaming G5/G7 gaming laptops equipped with 10nm Intel 12th Gen Processor today. A laptop to meet the wide range of needs in multitasking, gaming, and entertainment, with 12th Gen Intel Core i5-12500H laptop CPU, which is comprised of 12-core, 16 threads, and a maximum clock rate of 4.5GHz, to meet the needs for telecommuting and online classes, the purchase of high-performance laptops has been made easier with the adoption of Core i5-12500H, the Core i5 processor is powerful enough to effortlessly handle users' routines. Equipped with the graphics cards of NVIDIA GeForce RTX 30 Series, also introduces MUX switch graphics card switching technology, discrete GPU can be directly output to the display with just one click, which can easily improve the game performance and increase the frame rate in fierce game battles. For offering authentic gaming specifications and flexible expandability of hardware. The series can satisfy the user's needs for playing multiple roles in life.