Monday, October 5th 2020

AMD "Big Navi" GPU Die Pictured? Allegedly Measures 536mm²

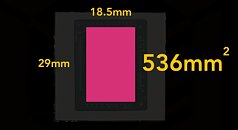

Coreteks, in a video presentation on Sunday, released what is possibly the very first picture of the AMD "Big Navi" GPU silicon, which could power the company's next-generation Radeon RX 6000 series flagship graphics card. The grainy, blurry-cam picture reveals a mostly square package with a large, rectangular die at its center, which Coreteks estimates to be 536 mm² in die-area, with 29 mm x 18.5 mm (LxW) dimensions. The channel used an unusual method for measuring the die size. The chip is rumored to feature around 80 compute units based on the RDNA2 graphics architecture, which includes fixed-function hardware for real-time raytracing, as RDNA2 is designed to meet DirectX 12 Ultimate logo requirements. We'll know more about the chip in the run up to its October 28 unveiling.

Source:

Coreteks (YouTube)

37 Comments on AMD "Big Navi" GPU Die Pictured? Allegedly Measures 536mm²

5700 is a shrink, try to make it on 16nm.

Who the f knows what it competes with, if you have FACT based proof rather than the wafts of air an ass puts out, please ,do show.

but if the infinity cache help to alleviate the performance drawback of a "Only" 256 bit bus for big Navi. this will do incredibly well with Integrated GPU that are even more bandwidth starved. if it's that, this litteraly mean a Jump in integrated GPU performance.

It could also explain why they did more of Vega APU while they were focusing on getting RDNA2 done.