AMD Radeon RX 7000 Series to Include 6nm Optical-Shrinks of RDNA2

AMD's upcoming Radeon RX 7000 series could include GPUs from both the RDNA3 and RDNA2 graphics architectures, according to reliable sources on social media. This theory holds that the company could introduce new 5 nm GPUs based on the new RDNA3 architecture for the higher end, namely the Navi 31 and Navi 32; while giving the current-gen RDNA2 architecture a new lease of life in the lower segments. This isn't, however, a simple rebrand.

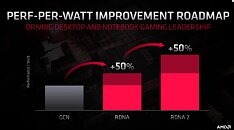

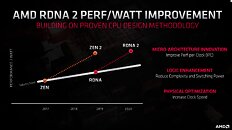

Apparently, some existing Navi 2x series chips will receive an optical shrink to the 6 nm node, in a bid to improve their performance/Watt. Some of the performance/Watt improvement could be used to increase engine clocks. These include the Navi 22, with its 40 RDNA2 compute units and 192-bit GDDR6 memory bus; and the Navi 23, with its 32 RDNA2 compute units and 128-bit GDDR6 memory bus. The updated Navi 22 will power the SKU that succeeds the current RX 6600 XT, while the updated Navi 23 works the lower-mainstream SKU RX x500-class.

Apparently, some existing Navi 2x series chips will receive an optical shrink to the 6 nm node, in a bid to improve their performance/Watt. Some of the performance/Watt improvement could be used to increase engine clocks. These include the Navi 22, with its 40 RDNA2 compute units and 192-bit GDDR6 memory bus; and the Navi 23, with its 32 RDNA2 compute units and 128-bit GDDR6 memory bus. The updated Navi 22 will power the SKU that succeeds the current RX 6600 XT, while the updated Navi 23 works the lower-mainstream SKU RX x500-class.