AMD "Renoir" Successor is "Cézanne," Powered by "Zen 3" and RDNA2

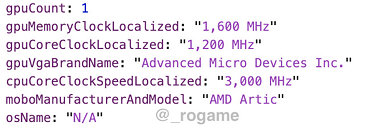

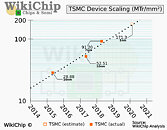

AMD's 7 nm "Renoir" silicon breathed life into the notebook processor market, by bringing 8-core/16-thread CPU performance into segments Intel reserved for 4-core/8-thread; and beat Intel in the iGPU performance front. 7 nm brought performance-Watt uplifts that spell serious competition for Intel across all notebook form factors, be it 15 W or 45 W. According to _rogame, who has a knack of getting far-out hardware rumors right, AMD has its successor on the drawing-board, and it's codenamed "Cézanne," after the French post-impressionist painter Paul Cézanne.

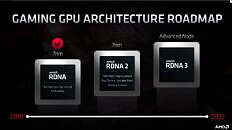

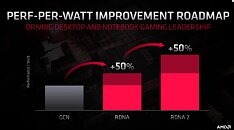

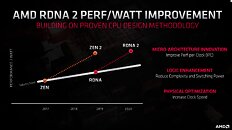

"Cézanne" could prove vital for AMD's foothold in the premium mobile computing segments as Intel is preparing to launch its 10 nm+ "Tiger Lake" processor soon, with advanced "Willow Cove" CPU cores, and Xe based integrated graphics. AMD plans to tap into its very latest IP. Although its core-count is not known, "Cézanne" will feature CPU cores based on the latest "Zen 3" microarchitecture. The iGPU will receive its biggest performance uplift in 3 generations, with an iGPU based on the cutting-edge RDNA2 graphics architecture that meets DirectX 12 Ultimate logo requirements.

"Cézanne" could prove vital for AMD's foothold in the premium mobile computing segments as Intel is preparing to launch its 10 nm+ "Tiger Lake" processor soon, with advanced "Willow Cove" CPU cores, and Xe based integrated graphics. AMD plans to tap into its very latest IP. Although its core-count is not known, "Cézanne" will feature CPU cores based on the latest "Zen 3" microarchitecture. The iGPU will receive its biggest performance uplift in 3 generations, with an iGPU based on the cutting-edge RDNA2 graphics architecture that meets DirectX 12 Ultimate logo requirements.